氮化镓( GaN) 高电子迁移率晶体管( high electron mobility transistor,HEMT) 以其击穿场强高、导通电阻低、转换效率高等特点引起科研人员的广泛关注并有望应用于电力电子系统中,但其高功率密度和高频特性给封装技术带来极大挑战。传统硅基电力电子器件封装中寄生电感参数较大,会引起开关振荡等问题,使 GaN 的优良性能难以充分发挥; 另外,封装的热管理能力决定了功率器件的可靠性,若不能很好地解决器件的自热效应,会导致其性能降低,甚至芯片烧毁。本文在阐释传统封装技术应用于氮化镓功率电子器件时产生的开关震荡和热管理问题基础上,详细综述了针对以上问题进行的 GaN 封装技术研究进展,包括通过优化控制电路、减小电感 Lg、提高电阻 Rg抑制 dv/dt、在栅电极上加入铁氧体磁环、优化 PCB 布局、提高磁通抵消量等方法解决寄生电感导致的开关振荡、高导热材料金刚石在器件热管理中的应用、器件封装结构改进,以及其他散热技术等。

一般禁带宽度大于 2 eV 的半导体称为宽禁带半导体也称为第三代半导体。氮化镓( gallium nitride,GaN) 作为第三代半导体材料,具有优异的材料特性,如禁带宽度大、击穿场强高、电子饱和漂移速率高等。GaN 电力电子器件主要以 GaN 高电子迁移率晶体管( high electron mobility transistor,HEMT) 为主。由于AlGaN/GaN 异质结界面存在高密度的二维电子气( 2DEG) ,所以 GaN HEMT 具有高电子迁移率、耐高温、耐高压、抗辐射能力强等优越性质,可以用较少的电能消耗获得更高的运行能力。这些特性使得电力电子系统朝着更高的效率和功率密度前进。

由于器件封装中的引脚及内部走线会引入寄生电感和电容,而氮化镓器件在高压大电流工况下开关过程中的 dv/dt 和 di /dt 极高,导致整个电路对这些寄生参数都极为敏感,甚至 nH 量级的寄生电感都很容易使器件发生高频振荡现象,使功率损耗增加,器件的可靠性降低。基于上述问题,出现了一系列新型的封装结构和电路布局以减小寄生参数,尤其是降低寄生电感。Chen 等分析了宽禁带半导体器件的开关特性、振荡种类,并总结了开关振荡的弊端,他认为开关回路的印制电路板( printed-circuit board,PCB) 布局和器件的封装对减小开关振荡至关重要。加入三代半交流群,加vx:tuoke08。Brothers 等研究了布局设计对器件寄生电感大小的影响。首先,横向布局的 GaN 芯片之间功率环路电感不对称,需要设计使用通量相消的路径来实现对称,使功率环路电感最小化。其次,安装带有分布式电容源的直流输入总线可以减小各相之间的相互影响和公用电感。Yu 等提出了一种三维集成无线键合模型,仿真结果表明相比于传统引线键合模型,无引线键合具有更低的寄生电感,并成功应用了 Ag-Ag 直接键合的方法,使该技术成为一种先进的倒装芯片互联技术。Lee 等提出采用功率四方扁平无引脚( PQFN) 封装的共源共栅( cascode) 型器件,该器件具有叠模结构、嵌入式外部电容和倒装芯片配置的特点。与使用相同 GaN 和 Si 器件的传统封装器件相比,其硬开关关断中的寄生振铃和软开关过渡中的开关损耗都有效减少。Chen 等提出 QFN-SiP 封装是目前减小寄生电感、实现高频电源设计的最优方案之一。通过将驱动器和 GaN 器件集成在同一个封装中,可以大大降低共源电感和栅极环路电感的影响。同时采用适当的 PCB 协同设计,可以进一步降低寄生电感。虽然宽禁带半导体器件可以提供更高的电流,但严重的电压和电流过冲阻碍了功率水平的进一步提高,这使宽禁带半导体器件的优势难以发挥。宽禁带半导体器件比 Si 金属氧化物半导体场效应晶体管( MOSFET) 具有更低的阈值电压和更快的开关速度,这对电子封装设计也提出了更高的要求。寄生电感仍然是目前电力电子器件封装亟待解决的问题之一。

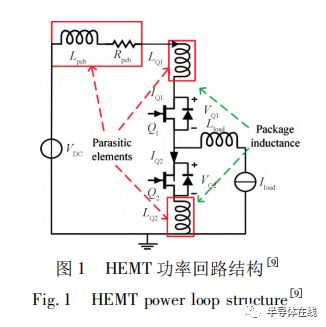

郝跃等对 GaN HEMT 的变温特性作了研究。发现栅极正向漏电随着温度的升高而增大,其原因是温度的升高提高了载流子翻越势垒的能力,材料方阻随温度上升近似线性的增大,从 20 ℃时的 442 Ω/sq 上升至 200 ℃时的 1 058 Ω/sq。方阻增大是由于升温时晶格振动散射增强,且方阻与 2DEG 密度和迁移率成反比,说明随温度升高会导致 2DEG 退化。HEMT 器件的饱和电流主要受迁移率和 2DEG 密度影响,因此温度升高会导致饱和电流和跨导下降。Egawa 等将 AlGaN/GaN HEMT 器件从 25 ℃升温至 200 ~350 ℃,器件跨导从 146 mS /mm 变为 200 ℃的 81 mS /mm 和 350 ℃下的 62 mS /mm。由此可见,高温会导致器件性能衰退,如何解决热耗散问题对 AlGaN/GaN HEMT 器件的发展尤其重要。陈堂胜等提出随着器件沟道异质结温度显著上升,器件输出功率密度降低,性能迅速恶化。可以说,散热问题已经成为制 GaN 功率器件技术进一步发展和应用的最大瓶颈。受衬底和外延材料本身导热能力所限,封装散热技术无法有效地解决这一问题,必须从 GaN 器件内部入手提升器件的热传输能力。基于此,本文综述了氮化镓功率器件封装产生寄生电感的原因、解决方法及其散热机理和路径,并对高热导率材料金刚石在 GaN HEMT 器件热管理中的应用研究现状进行了分析和讨论,以期为相关领域研究者提供借鉴和参考。Letellier 分析了 HEMT 功率回路的结构,包括电感 Lpcb和电阻 Rpcb及半桥和直流电压源,如图 1 所示。开关电流必须通过外部的铜材料( 印刷电路板轨道或电线) 且开关内部存在寄生电容及封装电感。随着开关频率的增 加,无源器件的体积减小,功率密度也会增大,高频情况下,会因上述参数变化引起寄生振铃,导致过电压、过度电磁干扰( EMI) ,甚至设备故障。

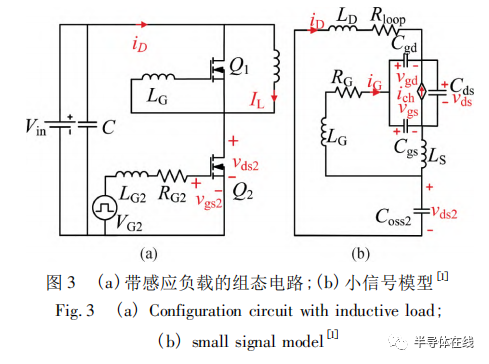

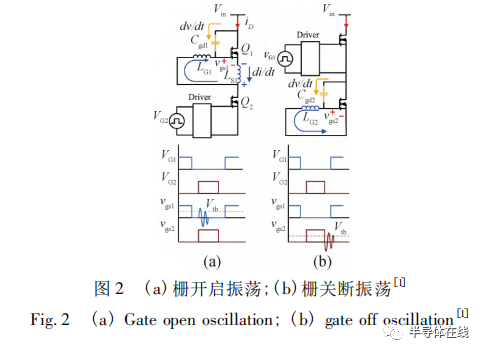

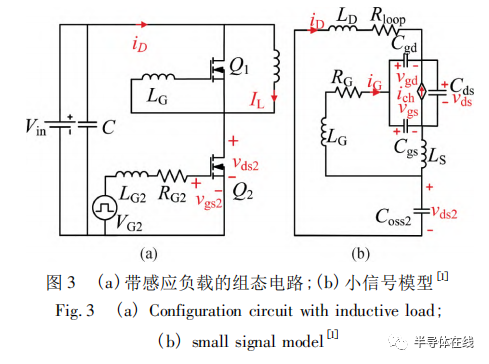

根据 Chen 等 分析,引起开关振荡的主要原因如下:( 1) 栅源电压的误开启触发振荡。宽禁带半导体器件的误开启主要是由高 dv/dt 和 di /dt 引起的,图 2展示了栅极开启和关断误触发的影响。开启时,顶部 Q1 栅源电压在 Q2 开启过程中逐渐增大,由于开关速度快,位移电流通过米勒电容 Cgd1被 dv/dt 诱导流向栅极结点,导致高栅源电压 Vgs1。同时高 di /dt 在共源电感 Ls1上产生负电压,产生误触发; 关断时,Q2关闭过程中,由于高 dv/dt 通过 Cgd2产生电压,其产生的电流通过 LG2产生电压,栅源电压超过阈值导致误导通。( 2) 源漏极电压持续振荡。由于氮化镓器件没有体二极管,当栅源或栅漏电压大于器件阈值电压时,电子被吸引到 AlGaN/GaN 异质结表面,2DEG 重建,产生反向电流。图 3 为带感应负载的组态电路及其小信号模型,当有源开关 Q2关闭时,负载电感电流 IL从源极流向漏极,可能导致栅漏电压超过阈值电压,此时由于氮化镓器件的寄生参数及反向导电特性,可能会发生持续振荡。当 Q2栅源电压正常时,则只考虑输出电容Coss2,当反馈系统满足巴克豪森稳定性判据时,系统将出现持续振荡。

开关振荡会导致电压电流过冲、击穿、电磁干扰以及额外的功率损耗,所以抑制开关振荡是提升器件性能的必要措施。

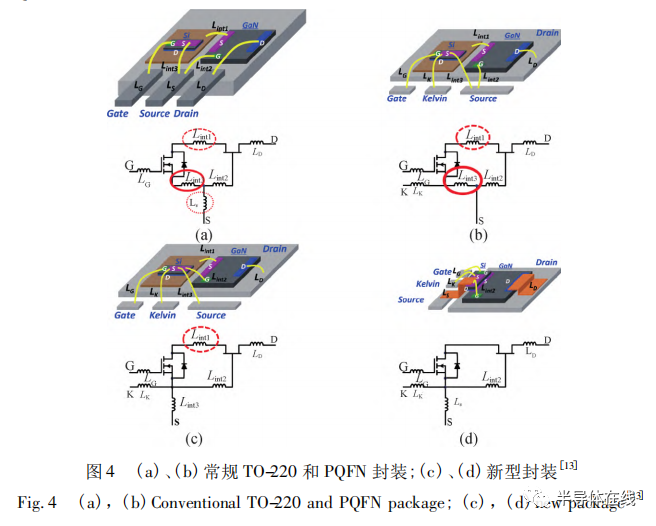

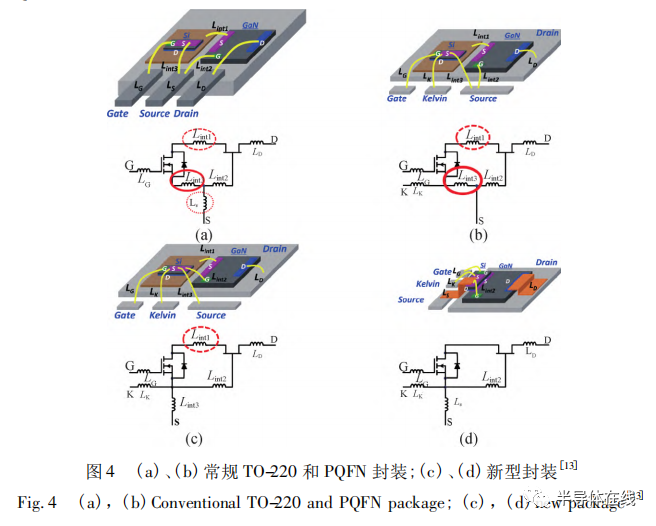

栅极上的电压振荡主要由寄生电感引起,所以降低寄生电感是抑制振荡的主要方法。Liu 提出了一种 PQFN PLUS 和 GaN HEMT 垂直低压 Si 功率 MOSFET 的叠模封装,如图4 ( a) 、( b)为常规的 TO-220 和 PQFN 封装,( c) 、( d) 为新型封装。如图 4( a) 中 TO-220 封装存在三种共源电感 Lint1、Lint3和 LS,PQFN 贴片封装的形式由于开尔文连接提供了单独的驱动回路,消除了 LS只能影响到 Si MOSFET,对 GaN HEMT 的影响有限。文中设计的 PQFN PLUS 主要区别在于重新定向了键合线 Lint2,这样 Lint3被排除在 HEMT 驱动回路之外,同时通过开尔文连接也被排除在 MOSFET 驱动回路之外,不再是共源电感。如图 4( d) 所示,文中所设计的 stack-die 封装中,将 MOSFET 的漏极直接安装在 HEMT 的源极顶部,使用这种叠层封装进一步消除了 Lint1。所以采用这种 stack-die 叠层封装可以消除所有共源电感,对 HEMT 的封装起到了优化作用。对比 PQFN 封装,降低了硬开关的开关损耗,提升了开关速度,开关关闭时寄生振铃减小。

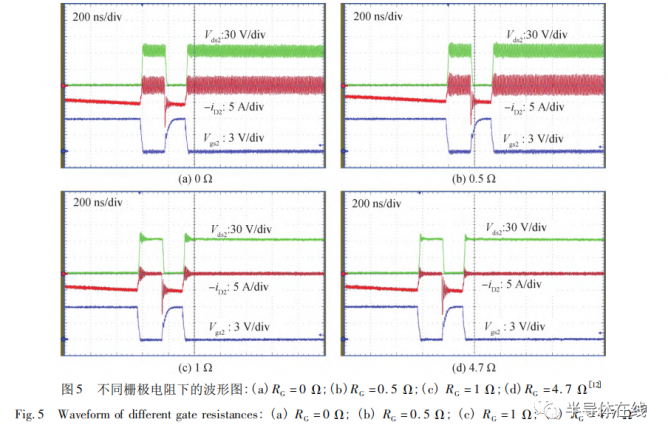

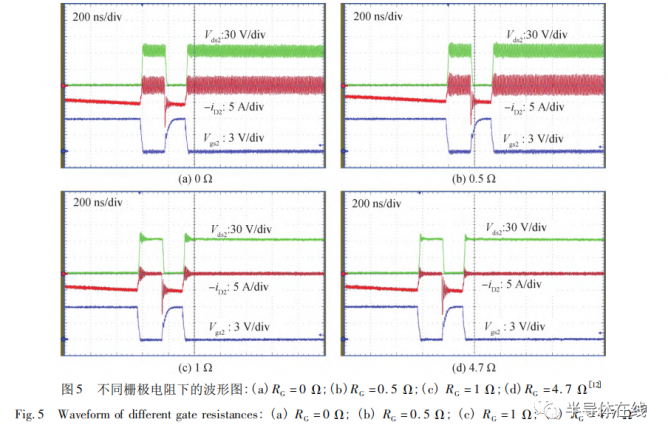

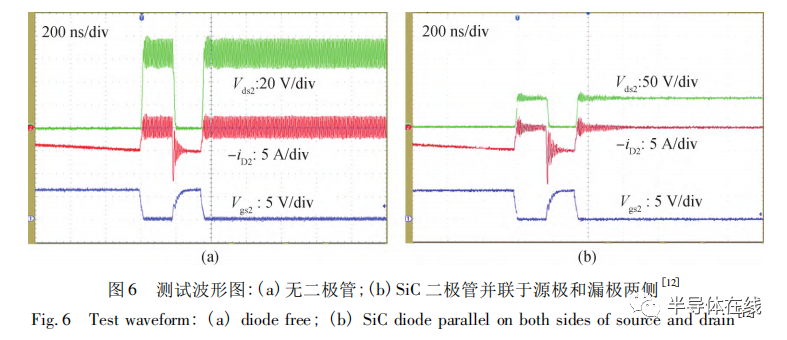

上述方法虽能有效降低共源电感,但叠层封装增大了封装体的厚度,相对来说体积更大,封装难度更高。Wang 等列举了三种常规解决开关振荡的方法,除了如上所述的减小共源电感外,还提到了增加栅极电阻来抑制振荡。如图 5 所示,驱动电压为 60 V,栅极电阻分别为 0 Ω、0. 5 Ω、1 Ω 和 4. 7 Ω。随着栅极电阻的增大,振荡频率也逐渐减小。在漏源极之间并联一个 SiC 二极管,二极管的结电容导致 Cds增加,从而达到抑制开关振荡的效果。然而实验结果表明,振荡不会在开始时就迅速衰减,这是由于二极管本身也会增加寄生电感,如图 6 所示。

在栅极上增加无源器件铁氧体磁珠也可以达到抑制振荡的效果。铁氧体磁珠等效于电阻和电感串联,具有很高的电阻率和磁导率,两者都与频率相关。高频时呈阻性,所以能在较宽的频率范围内提供较高阻抗,从而提高调频滤波的效果。磁珠与电感的区别主要在 于: 电感是将电能转换为磁 能,表 现 为 噪 声 或EMI; 磁珠是将电能转换为热能,不会对电路造成二次干扰。

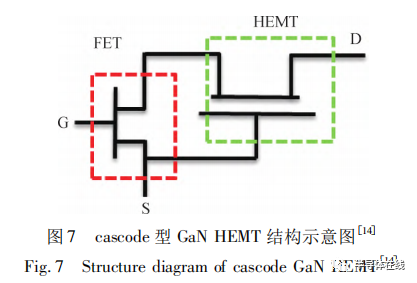

Wang 等展示了 transphorms 公司的 cascode 型GaN HEMT,包含一个低压常关型的 Si FET 和一个高压常开型的 GaN HEMT,结 构 如 图 7 所 示。在 低 侧MOSFET 上采用不同电阻值的铁氧体磁珠 ( 80 Ω、120 Ω和 430 Ω) 进行比较,开关波形如图 8 所示。

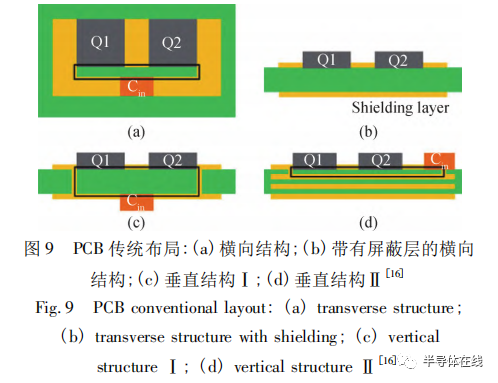

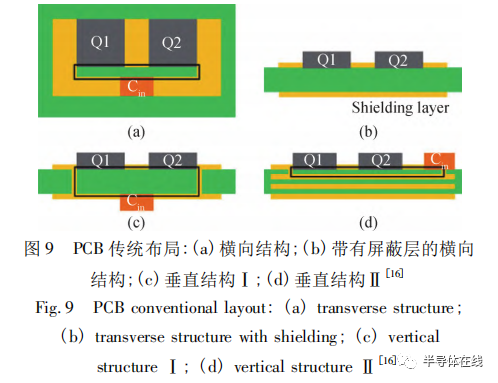

由图中结果可以看出阻值较大的磁珠有助于降低峰值电压,但会导致更长的开关时间。高频情况下,一般使用 120 Ω 左右的磁珠即可。PCB 板上的铜线会产生阻抗、寄生电感,这就意味着会产生功耗和热量。式中: R 为铜线产生的阻抗; ρ 为铜的电阻率; L 为铜线长度; S 为铜线截面积。可以通过控制走线的长度、厚度和宽度来降低阻抗,如栅极环路及高频环路应做到尽可能小,增大共源极减小漏极寄生电感以降低开关的电压电流应力,同时减小共源极增大漏极寄生电感以降低开关损耗。对于 PCB 布局,需要特别注意减小两个突出的回路电感: 栅回路电感和功率回路电感。栅回路电感会损害栅控安全,降低开关速度; 功率回路电感会增加晶体管漏源极电压的过射电压,影响工作可靠性,并导致额外的开关损耗。优化后的 PCB 布局可使功率回路电感最小化,提高器件工作效率。可以通过优化功率回路布局以减小寄生电感,布局可分为两类: 横向结构和垂直结构。

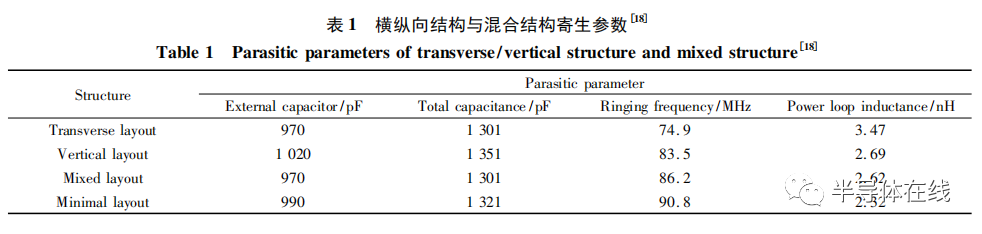

横向结构采用一个导电层,功率回路与导电层平行,如图 9( a) 所示。通过增加屏蔽层,可以减小功率回路的电感,因为屏蔽层中的涡流降低了磁通密度,如图 9( b) 所示。垂直结构中采用两个导电层,功率回路垂直于导电层。垂直结构有两种常用结构,图 9( c) 所示为一种垂直结构,其一侧为开关器件,另一侧为电容器。另一种垂直结构在同一侧有开关器件和输入电容,该垂直结构采用内导电层,减小了功率回路的面积,减小了功率回路的电感,如图 9( d) 所示。Sun 等对 HEMT 内部结构作了分析,HEMT 内部寄生电感模型如图 10 所示。图中 Q1 和 Q2 分别为高侧 GaN HEMT 和低侧 GaN HEMT 的等效电路。GaN HEMT 内部的寄生电容是开关工作时功率损耗的主要来源,其中输入电容( Ciss = CGS + CGD) 导致栅极损耗,输出电容( Coss = CGD + CDS ) 导致开关损耗。对如图 11所示的三种结构( ( a) 、( b) 、( c) ) 设计进行了双脉冲测试,发现纵向与混合设计比横向设计寄生电感降低 70%以上,但纵向设计受板厚和散热片放置的限制。在此基础上,提出了一种最小结构的设计,如图 11( d) 所示。横纵向结构与混合结构寄生参数如表 1 所示,纵向结构的功率回路电感比横向结构低 23. 4% ,验证了导通回路设计和去耦电容布置的重要性。在混合结构中,通过磁抵消进一步减小了功率回路的电感。最小布局的功率回路电感最小,因为其导通回路最短,仅为 2. 32 nH。该布局也可以很好地处理散热问题,计算得到异质结到环境之间的热阻为 29. 6 K/W。

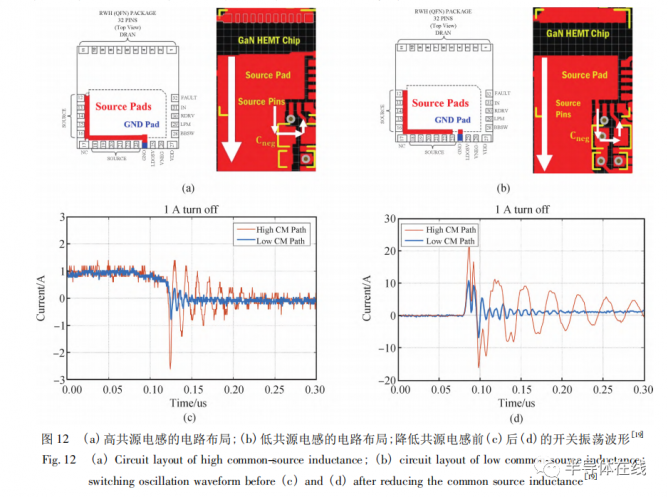

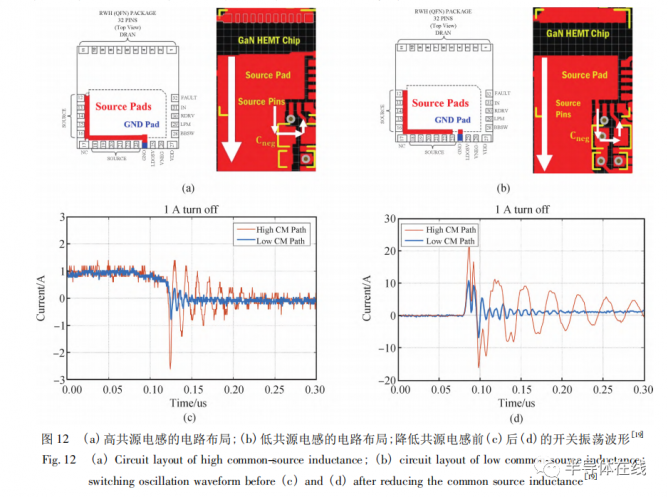

Abdullah 等提出一种直接驱动系统,简化了电路设计,减少了外部元件的数量,并且具有较小的栅极回路寄生参数。同时研究了改进开关瞬态特性的 PCB 布局优化方法,他指出: 为了实现高性能和平滑的瞬态切换,在芯片周围放置的无源元件必须优化,内部驱动电路运行所需的组件很少,重要的是要减少在器件开启和关闭过程中引起电流振荡的共源路径。图 12 为改进前后的 PCB 布局。图中 GND 引脚由内部连接到源极,之间的 Cneg是必要的,因为此路径上的共源路径若忽视,则会引起栅极处的强烈振荡。可以从外部将其分离,以避免电流耦合,如图 12( b) 所示。对比降低共源电感前后的开关振荡波形( 见图 12( c) ) ,可以看出有明显的优化。通过更优化的多层 PCB 板设计可以进一步改进。

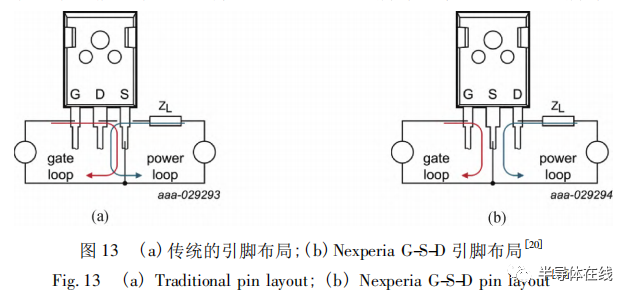

Nexperia提出一种新型引脚分布的封装形式。在直插式( TO-247) 封装中,漏极是栅极和功率回路的共同节点,为了使两个回路的耦合最小化,将原有的 G-D-S 引脚布局改为 G-S-D 引脚布局,如图 13 所示。

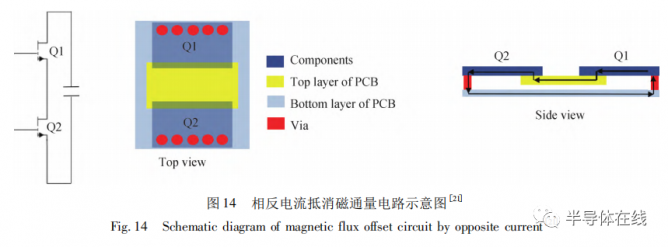

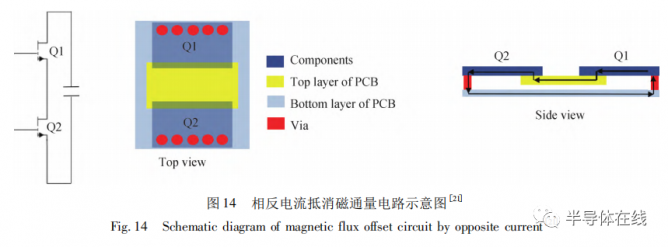

根据 GaN System 应用手册,当两个相邻的导体靠近而电流方向相反时,两股电流产生的磁通量就会相互抵消,这种磁通抵消效应可以降低寄生电感。因此 PCB 布局时,使高频电流在相邻的两个 PCB 层上以相反的方向流动,可以减小寄生效应,如图 14 所示。

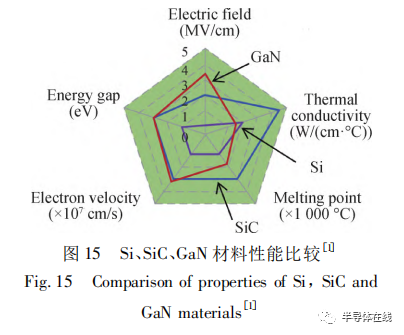

Yang 等提出了一种环路结构,设计环路结构时使每一层回路的电流方向都被设计成彼此相反的方向,以最大限度提高磁通抵消的效果。在相同面积下,采用所提出的垂直晶面环路结构,功率回路电感和栅回路电感比单回路电感减少 50% 。减小了寄生电感引起的振铃以及电压和电流的升降时间,还降低了开关损耗。综上所述,GaN HEMT 功率器件的高频特性,使 dv/dt 和 di /dt 所导致的开关振荡更加严重,主要原因取决于芯片内部及封装体产生的寄生电感。通过优化控制电路、减小 Lg电感( 振荡诱发的主要因素) 、提高 Rg抑制 dv/dt( 需要在抑制和开关速度之间折衷) 、在栅电极上加入铁氧体磁环、优化 PCB 布局、提高磁通抵消量等方法,可以有效减小开关振荡,提高器件的可靠性。所有电力电子设备在正常运行时都会产生大量热量,更快的开关频率和更高的电流密度意味着更大量的热循环。芯片异质结结温升高,会降低漏极电流,影响器件性能。随着电流密度的增加,由于器件运行产生的自热效应,通道温度会比环境温度高出几百度。自热效应会导致器件性能恶化甚至烧毁金属线,是降低器件寿命和可靠性的关键因素之一。如图 15 所示,图中对比了硅、碳化硅及氮化镓的材料性能。可以看出,氮化镓相对于碳化硅最大的缺点是热传导能力不足。

Harris 等分析了 GaN HEMT 瞬态升温曲线的测量结果,揭示了 HEMT 垂直方向的散热路径,并证明此路径由芯片连接材料及封装体本身为主导。因此需要更多区别于传统封装的手段来满足高频功率器件。基于此,产生了许多高温连接技术,如银烧结技术及许多新型的封装结构。

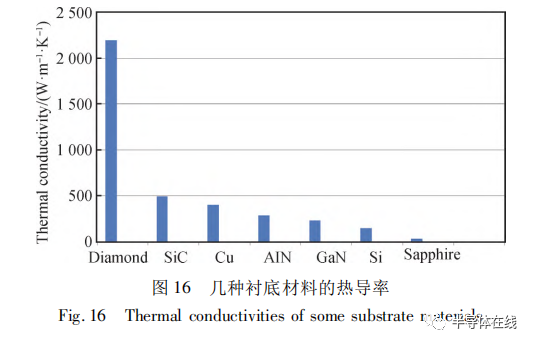

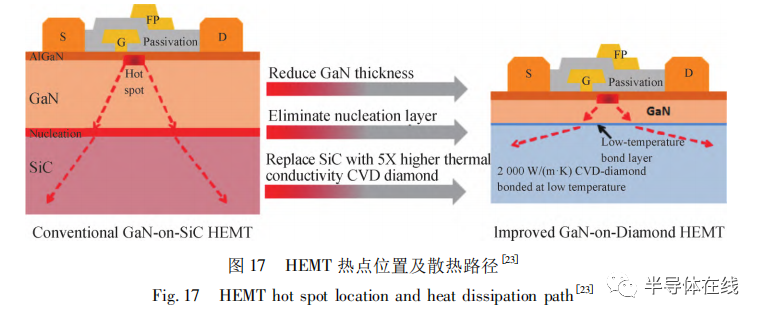

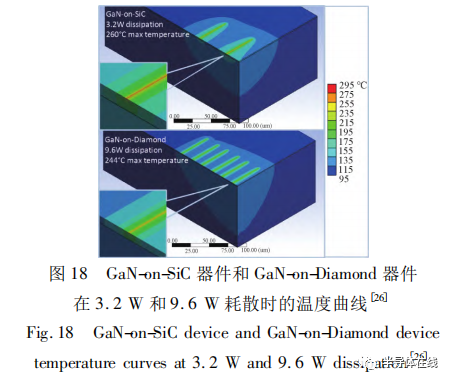

一种高导热、电绝缘的衬底是氮化镓高功率晶体管的理想衬底,如图 16 所示为几种衬底材料的热导率。由图可知,金刚石单晶的热导率最高,相比之下传统的 Si 或 SiC 衬底作为热沉衬底,虽能起到散热的作用,但两者的热导率( Si 衬底热导率 191 W/( m·K) ,SiC 热导率 490 W/( m·K) ) 较低,散热效果欠佳。通过化学气相沉积( chemical vapor deposition,CVD) 得到的多晶金刚石热导率可达 1 500 W/( m·K) ,是 SiC 的 3倍之多,并且绝缘性能较好,因此使用金刚石作为衬底可以有效解决 HEMT 的散热问题。HEMT 主要的热源在 2DEG 层产生,热点在栅极靠近漏极一侧,所以金刚石层越靠近有源区沟道层,散热效果越好,如图 17 所示为 HEMT 热点位置及散热路径。Chu 等采用 ANSYS 进行有限元建模,比较了 GaN-on-Diamond 和行业内标准 GaN-on-SiC 的热性能,结果如图 18 所示,在 3 倍的功耗下,新型 GaN-on-Diamond 器件的最大结温为 244 ℃,相比 GaN-on-SiC 器件降低了 16 ℃。

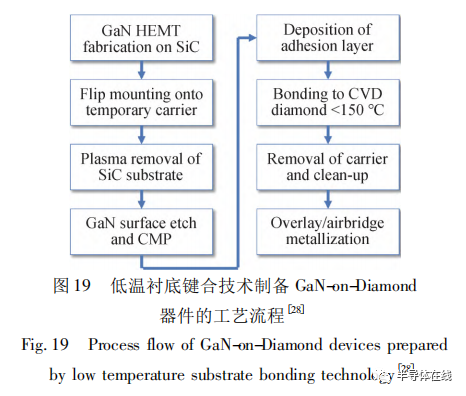

目前金刚石与 GaN HEMT 集成用于解决器件散热的研究中,较多的技术是将制备完成的 GaN HEMT 从原有衬底上剥离下来,转移键合到金刚石衬底上。转移键合的方法与直接金刚石生长技术相比,在灵活性方面具有显著优势。Chu 等将 GaN HEMT 从主体 SiC 衬底上剥离下来,然后通过低温键合工艺( 小于 150 ℃ ) 将其转移到多晶 CVD 金刚石衬底上,步骤如图 19 所示,得到的 GaN-on-Diamond HEMT 在 10 GHz( CW) 下,直流电流密度为 1. 0 A/mm,跨导为 330 mS /mm,射频输出功率密度为6. 0 W/mm。通过有限元热模型分析表明,与传统的 GaN-on-SiC 器件相比,其单位面积功率提高了 3 倍。

2015 年 Chao 等将峰值跨导提高到 390 mS /mm,最大漏极电流密度为 1. 2 A/mm。10 GHz( CW) 下射频输出功率密度为 11 W/mm,相比 SiC 衬底,功率密度提高了 3. 6 倍。2017 年 Liu 等实现了 3 英寸( 1 英寸 = 2. 54 cm) 的 GaN-on-Diamond HEMT,通过刻蚀 SiC 衬底转移键合,成品率超过 80% ,转移过程中观察到应变松弛现象,但并没有降低 2DEG 的密度,在功效( PAE) 为 50. 5% 的 10 GHz 条件下 GaN-on-Diamond HEMT 的最大电流密度为 1 005 mA/mm,功率密度为 5. 5 W/mm,异质结到封装体表面的热电阻降低了20% ,峰值温度从 241 ℃降至 191 ℃。2018 年 Gerrer 等利用范德瓦耳斯力键合氮化镓和金刚石,使两个表面紧密接触,再进一步退火使两个表面结合更加紧密。2018 年 Mu 等首次采用改性表面活化键合( SAB) 的方法,实现了氮化镓和金刚石的室温键合。并采用扫描透射电子显微镜( STEM) 和 X 射线谱( EDX) 分析了键合界面的微观结构和成分,结果表明,界面结合均匀,无纳米空洞。2020 年 Motala 等提出了使用二维氮化硼释放层,通过范德瓦耳斯力和聚合物黏合剂中间层,将 AlGaN/GaN HEMT 向任意基底转移。转移过程中没有观察到器件退化,相比于 Si 衬底,转移到 SiC 衬底上器件温度显著降低。降低聚合物黏合剂的厚度,器件在 600 mW 工况下,运行过程达到了与生长晶圆相当的峰值温度,表明优化聚合物层可以进一步提高输出性能。该技术为金刚石基 HEMT 的转移键合提供了很好的参考。

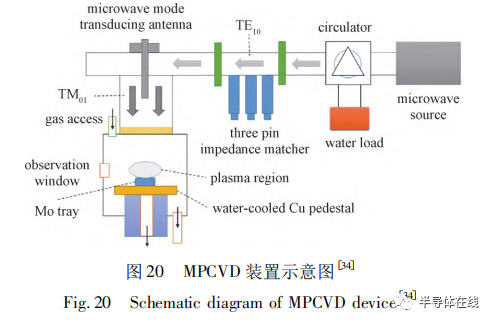

键合技术虽然较为简单成熟,但受限于多晶金刚石加工难度大、粗糙度大的问题,并且直接键合难以实现,目前大多是采用键合层的方法键合,但键合层的热阻也较大。因此,直接在 GaN 基半导体上外延多晶金刚石也是解决半导体材料散热的方法之一。目前,人工合成金刚石技术主要有两类: 一类是高温高压( high temperature and high pressure,HPHT)法,另一类是 CVD 法。如图 20 所示为微波等离子体化学气相沉积( microwave plasma chemical vapor deposition,MPCVD) 装置简图,MPCVD 法是利用微波将气体分解,在合适温度的基片上沉积金刚石膜,其无阴极放电的特点避免了热丝、电极等对金刚石膜的污染,同时等离子体相对稳定,因此 MPCVD 法可以制备优质的金刚石膜。目前该方法是制备高品质金刚石膜的最有效方法。

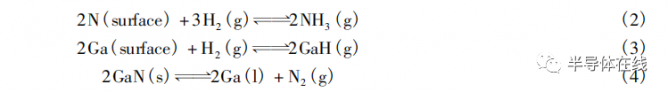

直接在 GaN 上生长金刚石的问题在于: CVD 金刚石工艺条件下 GaN 不够稳定,导致 GaN 薄膜被刻蚀。虽然 GaN 本身的熔点为 2 500 ℃左右,但 MPCVD 是利用 CH4 /H2气体混合物高温高压下形成等离子体来沉积金刚石,GaN 与氢等离子体在 800 ℃条件下就会发生反应,GaN 固体本身也同时会发生分解现象。反应方程式如下:

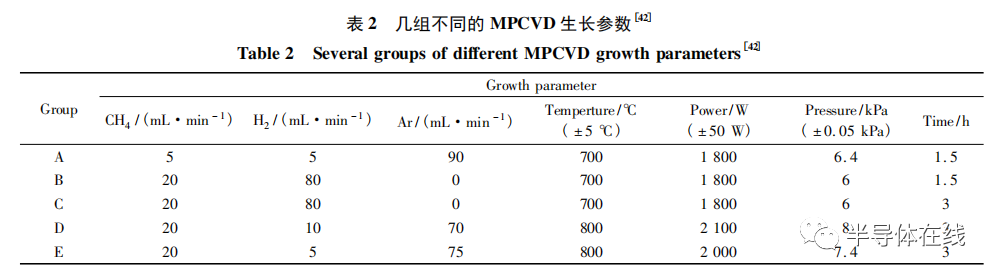

Tiwari 等研究了微波氢等离子体对 GaN 的刻蚀,SEM 照片表明刻蚀坑呈六角形,平均尺寸大于 200 nm,AFM 照片表明刻蚀大小和深度会随时间和压力的增加而增加。为此,Mccauley 等和 Petherbridge 等分别提出用 Ar/CH4和 CO2 /CH4促进金刚石低温沉积。May 等提出在反应过程中通入氮气来抑制上述可逆反应,然而导致了金刚石膜质量低、多孔、附着性差等问题。Yamada 等研究了氮原子的引入与衬底温度的耦合效应,研究表明氮元素浓度不是导致质量下降的根本原因,即使在氮元素分布均匀的情况下,金刚石拉曼光谱的半峰全宽也会随着厚度的增加而增加,衬底温度的控制更加关键。国内目前已实现在 50. 8 mm( 2 英寸) 硅基氮化镓异质结半导体材料上采用低压等离子体化学气相沉积方法淀积 100 nm 厚度的氮化硅材料作为过渡层和保护层,有效调控了材料应力,保护氮化镓基材料在多晶外延过程中不被氢等离子体刻蚀。然后采用微波等离子体化学气相沉积设备在氮化硅层上方实现多晶金刚石材料的外延生长,生长速度可以达到 150 μm /h,实现了( 001) 面和( 111)面原子级平整表面的单晶金刚石的沉积。林晨等在 Si 衬底上用 MPCVD 方法在多组条件下生长出不同样品并对其形貌和成分进行了表征,如表 2 所示。从表征结果的对比分析发现: A ~ E 组样品连续成膜面积逐渐增大,但薄膜中存在较多孔隙,说明表面预处理工艺的均匀性仍需优化改进; 随着碳源气体浓度的增加和 H2比例的减少,样品生长速率逐渐增加,其中 E 组样品生长速率最高,约为 0. 75 μm /h。

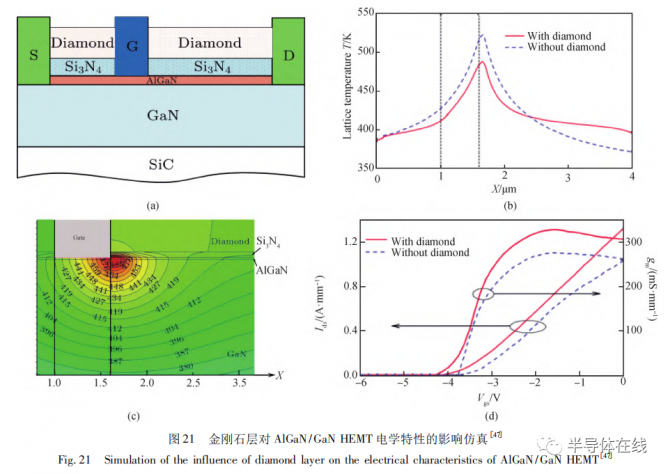

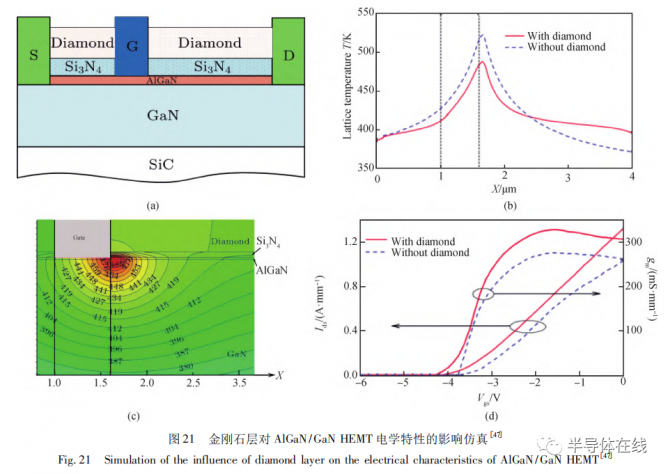

除了在 GaN 表面外延的金刚石质量会影响散热效率外,金刚石和氮化镓材料间的界面热阻( TBR) 也是一项重要的参数。界面热阻又称边界热阻,出现在不同介质之间的界面处,会阻碍热流的传输。其定义为界面处的温差与流过该界面的单位热流之比。热量会在微纳结构芯片和复合热界面材料内部的纳米界面处发生大量的声子散射,大幅阻碍热流传输和扩散,所以 TBR 对电子器件的散热问题起着至关重要的作用。Yates 等分别测试了插入 5 nm 的氮化铝和氮化硅及没有插入层时,氮化镓和金刚石的 TBR 大小,利用时域热反射和电子能量损失谱,发现在氮化硅插入层上外延金刚石所得到的 TBR 最低。这是由于在界面上形成的 Si-C-N 层避免了氮化镓分解。无插入层和氮化铝插入层的样品由于界面粗糙度变大,增强了声子散射,从而增大了 TBR。Sun 等结合瞬态热反射测量、有限元建模和微观结构分析,发现金刚石与氮化镓的TBR 主要与用于金刚石种晶的氮化硅插入层的厚度和成核层的质量有关。插入层越薄,成核质量越好,TBR 越小。Pomeroy 等将插入层厚度从 90 nm 降低到 50 nm,TBR 从 41 ( m2·K) /GW 降低到 17 ( m2·K) /GW。而 Cho 等采用 30 nm 的 SiN 层获得了 29 ( m2·K) /GW 的 TBR,说明金刚石成核层的质量也是决定因素,单一地减小插入层的厚度无法最大限度地减小 TBR。由上所述,HEMT 自热效应主要由沟道 2DEG 产生,热点靠近栅极偏漏极一侧。所以,金刚石散热层如果不作为衬底而是作为更加靠近沟道位置的盖帽层,散热效果会更加显著。Zheng 等通过仿真研究了金刚石层对 AlGaN/GaN HEMT 电学特性的影响,图 21 为器件结构及带有金刚石层的 AlGaN/GaN HEMT 中晶格的温度分布情况及金刚石层对 HEMT 电学特性的影响。可以看出,热点位置仿真结果与理论分析一致,温度峰值点从无金刚石层的 523 K 降到了 488 K。与常规 HEMT 相比,带有金刚石层的 HEMT 阈值电压明显减小,且跨导增加,这可能是由于在较低的晶格温度下,借助于金刚石层,沟道电子迁移率增加。金刚石薄膜厚度在 1 μm 以下时,fT随着薄膜厚度增加的增长迅速增大,薄膜厚度增加到 1 μm 以上后趋于饱和,由 24. 4 GHz 提高至 31. 5 GHz,提升了 29% ,因此金刚石层是提高器件高频性能的一种有效手段。Anderson 等实现了上述器件结构,测试得到沟道温度下降 20% ,电学性能得到改善,导通电阻和击穿电压显著提高,栅极漏电流减小。进一步改进直接在氮化镓表面生长沉积的工艺,钝化效果与传统的 SiNx钝化器件效果一致。在此基础上,Zhang 等用有限元方法研究了金刚石层对多指 HEMT 的影响。结果表明,金刚石层可以大大降低结温,且近结区温度变得更加均匀。金刚石层的散热效率随厚度的增加而增加,但增长速率有减缓的趋势。假定热边界电阻( TBRs) 为 1. 5 × 10 - 8 m2·K·W -1,栅长 20 μm,栅极功率密度为 6 W/mm 的 12 指 GaN-on-Diamond HEMT,20 μm 的金刚石散热层可以使结温从 195. 8 ℃ 降低到172. 2 ℃。在 SiC 衬底上的 HEMT 的温度降低更为显著,可达 25. 3% 。Zhu 等首次通过 Sentaurus TCAD模拟研究了金刚石层对双通道 AlGaN/GaN HEMTs 的影响。结果表明,当功耗增加到 46 W/mm 时,金刚石层厚度为 1 μm 的双通道 AlGaN/GaN HEMTs 的峰值温度可降低 64 K,饱和漏极电流和跨导分别提高了0. 21 A/mm和 22 mS /mm,峰值 fT和 fmax分别提高了 4. 7 GHz 和 10. 3 GHz。

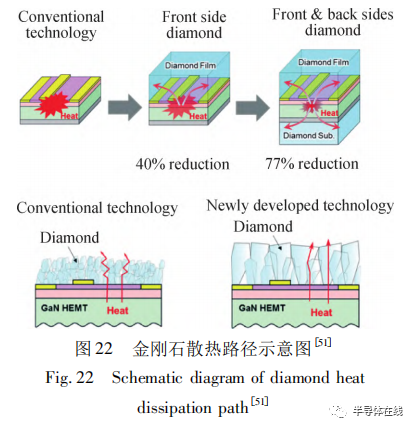

日本富士通公司成功开发了世界上第一项用于在GaN HEMT 表面上生长具有高效散热性能的金刚石膜技术。将直径为几纳米的纳米金刚石颗粒放置在装置的整个表面上,然后将纳米金刚石颗粒暴露于具有高热能的甲烷气体中,以此将甲烷气体中所含的碳转化为金刚石,然后将其掺入颗粒中,碳以其高能量被选择性地掺入指向特定方向的金刚石中,避免了纳米金刚石沿不同晶向生长阻碍热量散出,且实现了上下双层金刚石散热技术,相比单层实现了 77% 的温降,如图 22 所示。

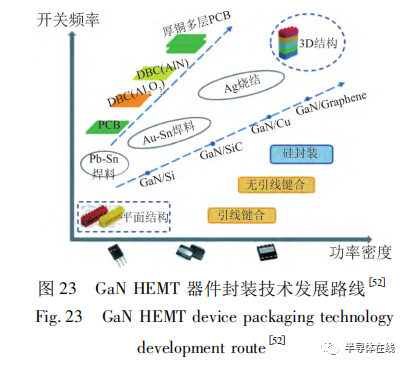

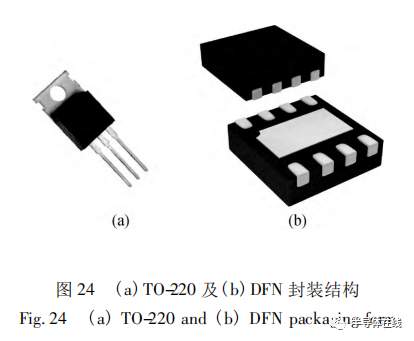

由上可知,金刚石层可以对晶格温度进行调控,使温度更加均匀,从而扩大器件的横向热传导路径,有效抑制器件自热效应引起的晶格温升和器件性能的下降,为GaN HEMT 在高功率运行下的热设计提供了新的路。不同类型的 GaN 功率器件,根据其内部电路的拓扑结构以及功率等级差异,需要选择不同的封装类型及结构,以保证其优异的电、热性能得以充分发挥。采用的封装形式应在设计集成电路时加以考虑,其中考虑的因素包括管脚数、腔体的尺寸、引脚尺寸、封装的体积、散热性能和封装类型。封装类型分为通孔直插式和表面贴片式,两种封装技术大为不同,各有优缺点。鲍婕等从 GaN 芯片衬底、芯片与基板互连、基板等封装材料、封装结构以及工艺等角度总结了 GaNHEMT 器件封装技术发展路线。总体趋势是从引线键合的平面封装向无引线的立体封装发展,如无引线的平面式结构、嵌入式结构、晶圆级扇出型结构以及 3D 堆叠结构等; 基板从 PCB 到 DBC 再到二者的混合结构,如图 23 所示。技术上提高封装中各层材料的热导率,在减小寄生电感的同时实现有效散热,尽可能兼容成熟的硅加工技术以降低产品成本,为当前研究的重点内容。GaN HEMT 封装分为塑封类和陶瓷类两种,其中塑封类包括直插式 TO 系列、引脚表面贴装系列、无引脚的 DFN、QFN、LGA 系列等; 金属和陶瓷类包括 TO 系列、SMD 系列和 CLCC 系列等。目前 GaN HEMT 在驱动系统中使用时一般采用 LGA 封装,可以减小寄生电感和电阻,其他大多数采用的是 TO-220 及 DFN( 双边扁平无铅封装) 封装,如图 24 所示。

两种封装形式各有优缺点,TO-220 封装是大功率晶体管、中小规模集成电路常采用的一种直插式封装形式。分为全包( 塑封) 和半包( 铁封) 两种,其中塑封封装可以实现散热片和外部的电绝缘,铁封封装的散热效果则更好,可以满足电路灵活设计和不同需求。相比贴片式封装,直插式封装散热效果更好,方便增加

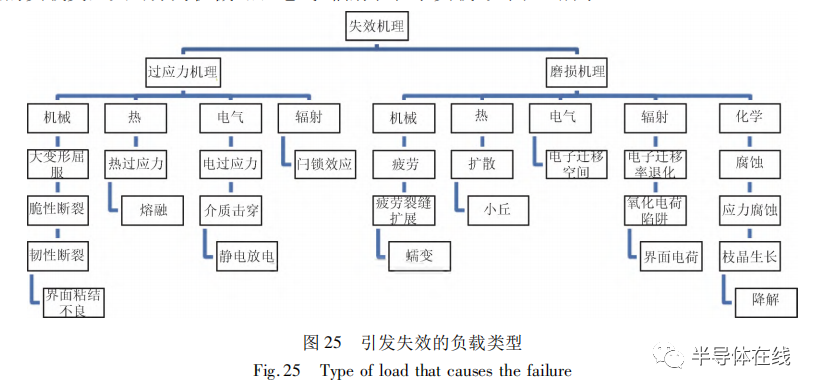

散热装置或其他主动冷却设备,且封装质量易测试。但由于其外引脚设计,导致其封装体积较大,且过长的引脚会引入不必要的阻抗容抗,导致开关振荡等问题。DFN 是目前最新的一种表面贴装电子封装工艺,PCB板的设计需要遵循相应的规则。DFN 封装尺寸小、I/O 数量少节省空间,可减少热路径,具有非常低的阻抗、自感,可满足高速或者微波的应用。但其焊接点质量只能通过 X 光检查,无法使用自动光学检测( AOI) ,因为焊接点只存在于封装塑料主体下方。电子器件封装过程十分复杂,其过程中产生的缺陷也很多。封装失效机理可分为过应力失效和磨损失效,失效的负载类型又可分为机械、热、电气、辐射和化学负载,如图 25 所示。

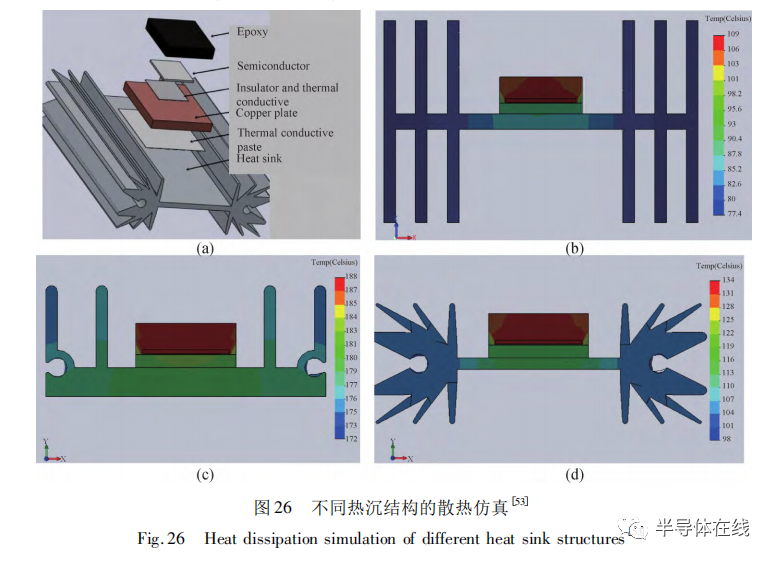

芯片散热主要有三种传播路径: 传导、对流和辐射,其中 80% 的热量都是通过封装体传导。热量从芯片经由键合材料( 芯片与背面露出框架之间的黏接剂) 传导至背面框架( 焊盘) ,然后通过印刷电路板上的焊料传导至印刷电路板。然后,该热量通过来自印刷基板的对流和辐射传递到大气中。其他途径还包括从芯片通过键合线传递到引线框架、再传递到印刷基板来实现对流和辐射的路径,以及通过芯片封装来实现对流和辐射的路径。封装框架通过焊料贴合在一个微型散热片上用来冷却芯片,这个微型散热片称为热沉。热沉的表面积对散热效果有很大影响,热沉表面积增大,其与空气之间的热阻减小,热阻与热沉面积的关系如式( 5)所示:

式中: Rhs-a为热沉与空气间的热阻; α 为对流系数; A 为热沉总面积。如图 26 所示为 Färcaş 等用 Solidworks 对三种结构不同的热沉的散热情况进行了模拟,对流系数为15 W/( m2·K) ,P = 13 W,环境温度 60 ℃,导热浆料为 Jetart 纳米银,导热系数为 4. 5 W/( m·K) 。显然热沉结构与空气接触的表面积越大,散热效果越好。

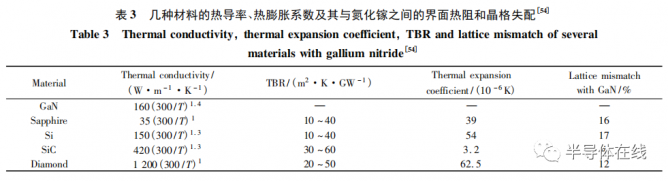

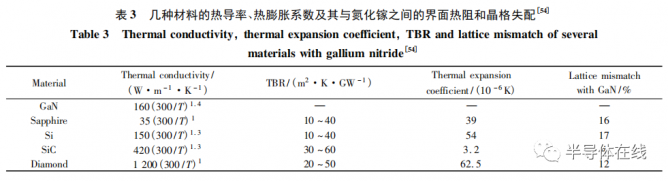

在没有外部散热器的情况下,最有效的散热路径是通过 PCB 的铜板与空气的对流。所以将衬底更换为导热率更高的材料也可以提高器件的散热性能,但目前从金刚石材料制备的研究状况来看,实际应用还需要一段时间。从表 3可以看出,碳化硅材料的热导率及其和氮化镓之间的 TBR 仅次于金刚石,且与氮化镓间的晶格失配小。GaN-on-SiC 器件可以在高电压和高漏极电流下运行,相同耗散条件下,SiC 器件的可靠性和使用寿命更好。碳化硅衬底根据电阻率的不同分为导电型和半绝缘型两类,分别外延沉积碳化硅和氮化镓后,用于功率器件和射频器件的制作。产业界用于功率器件制作的导电型碳化硅衬底以国外美国科锐 Cree、贰陆公司(Ⅱ-Ⅵ) 、道康宁( Dow Corning) ,德国 SiCrystal( 被日本罗姆 Rohm 收购) 等公司比较领先。国内企业有天科合达、山东天岳,但市场占有率较低,科锐占据导电型 SiC 衬底市场 62% 的份额。目前受限于衬底制造技术,仍然只能停留在 4 英寸与 6 英寸晶圆,8 英寸还未推广。

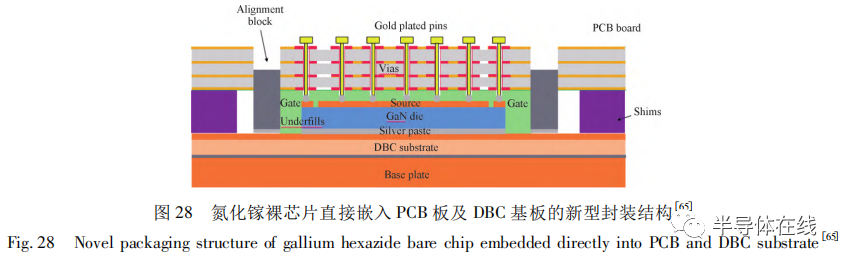

Qromis 公司设计了200 mm QST 衬底专利产品,该材料是一种聚合氮化铝,其热膨胀系数与 AlGaN/GaN外延层热膨胀非常接近,为实现非常厚的 GaN 缓冲层提供了路径,包括通过大于 100 μm 的快速生长外延层实现自立式和非常低的位错密度 GaN 衬底,有望用于 900 ~ 1 200 V 器件的缓冲层,使得商用垂直 GaN 功率开关器件和整流器适用于高电压和高电流应用领域。该公司还与比利时微电子中心 IMEC 合作,开发出高性能增强型 p-GaN 功率器件,其阈值电压可达到2. 8 V。Genns 等成功在200 mm QST 衬底上制备出 650 Vp-GaN HEMT,阈值电压高达 3. 6 V,导通电阻为 15 Ω·mm,150 ℃工况下,漏级关态漏电流小于 1 μA/mm。Yan 等将石墨烯覆盖在碳化硅衬底的 AlGaN/GaN HEMT 上,使用微拉曼光谱法测得器件热点温度下降了 20 ℃。Li 等将氮化镓键合到多层石墨烯构成的高导热复合材料( GC) 上,估算出 GaN/GC 间的热边界电导( TBC) 为 67 MW/( m2·K) 。与市面上的 GaN-on-SiC 和 GaN-on-Si 晶体管相比,GaN-on-GC 功率晶体管表现出优越性,并且热性能得到大幅改善。Mohanty 等通过深度反应离子刻蚀将 Si 基 HEMT 衬底刻出微沟槽结构,然后用电镀工艺填充高导热材料铜,提升了器件的散热性能。其饱和电流提升了 17% ,热点温度可降低 22 ℃。Zhao 等利用电镀技术成功将 HEMT 从 Si 衬底转移到铜基片上,表面形态几乎未受影响且不存在较大的应力,与 Si 上的电特性相同,但具有更好的散热性能。Wang 等采用层转移的方式制备了柔性的 HEMT,并通过电镀与 150 μm的铜膜集成,研究了 HEMT 的应变效应。在弯曲向下和弯曲向上的测试条件下,分别测得电流变化量为3. 4% 和 - 4. 3% ,阈值电压也发生了改变。这表明施加应变引起的压电极化电荷改变了沟道中 2DEG 的密度,从而导致漏极电流的变化。如果使用较大的压电负常数的材料作为势垒层,则极化电荷变化更大,电流调制也更大。美国德州仪器公司( TI) 设计了一款顶部冷却 QFN 封装结构,其顶部有一个暴露的铜热板,通过将散热器或冷板直接贴合在封装顶部实现。不仅为器件提供有效的散热通道,同时降低了 PCB 板上的应力,测试其热阻可降低 20% ~ 30% 。Cheng 等设计了一种在 Si 衬底上集成 V 槽铜基和 TO-3P 引线框架的 HEMT 新型封装结构,如图27 所示。与传统封装相比,V 形槽基板不仅为横向导热提供了额外的热通道,还可以实现精确定位。该显微组织为满足热要求而进行表面冷却,并在相似的封装尺寸下获得了比普通金属更低的封装热阻。当芯片通过导电涂料到铜基的热阻降低时,晶体管侧的热扩散得到改善。在相同的驱动条件下,与 DIP 封装相比,该方法的热阻降低了 19. 6% 。Lu 等设计了一种新型封装,将氮化镓裸芯片直接嵌入 PCB 板及 DBC 基板之间用于热提取,使用无压银烧结连接设备终端。封装结构如图 28 所示,并通过制备( 650 V,150 A) GaN HEMT 的单片封装和双片半桥模块验证了该方法。封装的仿真结果显示功率回路寄生电感小于 0. 5 nH,结点到外壳的热阻小于 0. 2 ℃ /W。

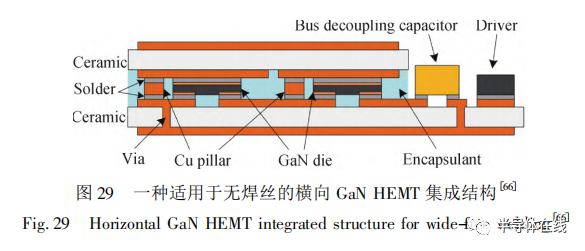

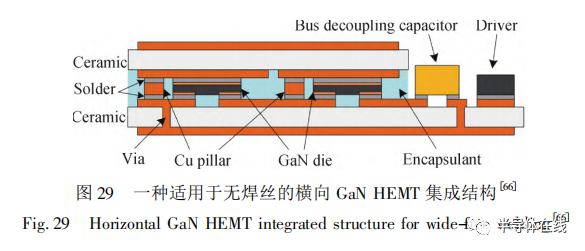

Li 等提出了一种适用于无焊丝的横向 GaN HEMT 集成方案。采用双面 DPC 基片和多铜层结构。如图 29 所示,氮化镓芯片夹在两 DPC 基板之间,以实现双面冷却。通过优化布局,采用磁场抵消和屏蔽层技术进一步降低寄生参数。由于增加了陶瓷基板,该结构相比传统键合线结构可以承受更高且更少的热机械应力。以此制备的 650 V/30 A 功率模块,与传统单面散热模块相比热阻降低 30% ~ 48% ,功率回路和栅回路电感降低到 0. 94 nH 和 2 nH,漏源电压最大 dv/dt 可达 150 V/ns,功率密度为 820 W/in3,峰值功率达到98. 85% 。

传统功率半导体器件互联技术一般采用无铅钎料或 Sn 基含铅的热界面材料,将热沉、基底和器件紧密结合在一起,再通过铝线或金线键合,但这些材料都不适合在高温工作条件下使用。主要原因是材料会因温度的大幅度变化发生蠕变造成焊点失效,或合金材料使半导体与元器件之间产生热应力导致损坏。一种导热率高且抗疲劳的热界面材料对器件的散热效率也是至关重要的。低温烧结纳米银糊因其较高的熔化温度,比传统焊料和胶膜具有更好的热/电导率,可用于需要高温操作和高散热能力的芯片连接。

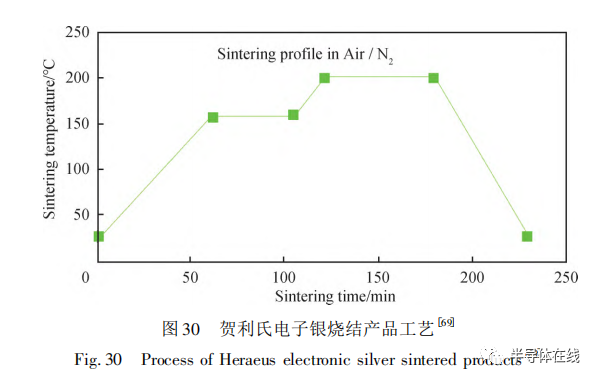

与传统焊接工艺和焊料相比,银烧结技术与出色的导热性能结合,可将可靠性提高 4 倍。纳米银的主要特点就是低温烧结、高温工作,烧结温度可低至 150 ℃,甚至室温。且金属银具有高的热导率和良好的导电性,以及抗腐蚀性和抗蠕变能力。纳米银焊料焊芯的结温比 AuSn 钎料低近 20 ℃,约下降 16. 7% 。Yu 等对无压低温固化纳米银钎焊膏的剪切强度、孔隙率和导热系数进行了研究。实验结果表明: 纳米银焊接件的平均剪切强度为 3. 65 MPa。纳米银钎焊的芯片空隙率小于 10% 。纳米银钎焊结合层的导热性能优于共晶( Au80 Sn20 ) 焊料。经过 100 倍的温度冲击试验( - 55 ~ + 125 ℃ ) ,功放元件性能稳定,无分层、输出功率降低等性能退化。因此,纳米银钎焊膏作为大功率器件的黏接材料,具有可靠的连接强度、良好的导热性和导电性。贺利氏电子 mAgic DA295A 无压烧结银使用微米级片状银粉来烧结,如图 30 和表 4 所示,与纳米粉相比,此工艺确保了更高的良率和更宽的工艺窗口及更低的成本,烧结温度低至 200 ℃,且达到低于 5% 的空洞率。

AlGaN/GaN HEMT 器件是重要的电力电子器件之一,由于其高频、高功率密度等特性,有着广泛的应用前景,但其可靠性仍然会受到封装体寄生效应、散热问题的影响。本文综述了国内外对于 GaN HEMT 器件降低寄生电感及封装散热关键技术问题的研究现状,为充分发挥 GaN 材料的优良特性,提高 GaN HEMT 器件的可靠性提供了有价值的参考。基于金刚石出色的导热性能,将其应用于 GaN HEMT 器件中可以实现有效的散热,本文对目前的应用研究成果进行了分析和讨论,对高导热金刚石材料增强 GaN HEMT 器件可靠性的研究具有一定的指导意义。针对功率器件可靠性的相关问题,GaN 基 HEMT 可以从以下几方面继续取得突破进展: ( 1) 针对不同类型的开关振荡,研究不同的解决方案,减少过冲及 EMI。通过设计更加优化的 PCB 布局,以减轻或抑制开关振荡。( 2) 设计新型的热沉结构或散热材料,使散热层更加靠近热点位置,进一步降低 TBR,增强器件横向散热性能。总之,氮化镓电子器件商业化产品虽然已初步应用,但仍有很大的发展空间,有待深入研究。若能更好地解决以上器件的可靠性问题,GaN 基 HEMT 器件将不仅在功率器件、微波器件领域,而且在传感探测、信息通信、航空航天等领域都有着巨大的发展空间和应用前景。

冯家驹1,2,范亚明2,3,房 丹1,邓旭光2,于国浩2,魏志鹏1,张宝顺2 ( 1. 长春理工大学,高功率半导体激光国家重点实验室,物理学院,长春 130022;2. 中国科学院苏州纳米技术与纳米仿生研究所,苏州 215123;3. 江西省纳米技术研究院,纳米器件与工艺研究部暨南昌市先进封测重点实验室,南昌 330200)