半导体产业网获悉:在刚刚结束的第37届功率半导体器件与集成电路国际会议(IEEE ISPSD 2025,全称为:IEEE 37th International Symposium on Power Semiconductor Devices and ICs)上,深圳大学射频异质异构集成全国重点实验室、材料学院刘新科研究员团队的三项研究成果入选, 其中一篇为口头报告,两篇为海报。IEEE ISPSD是功率电子器件领域全球最具影响力的顶级学术会议,被誉为功率半导体界的“奥林匹克”,本届会议于2025年6月1日-6月5日在日本熊本举办。

图1.参会人员集体合照。

本次入选的三篇论文工作如下:

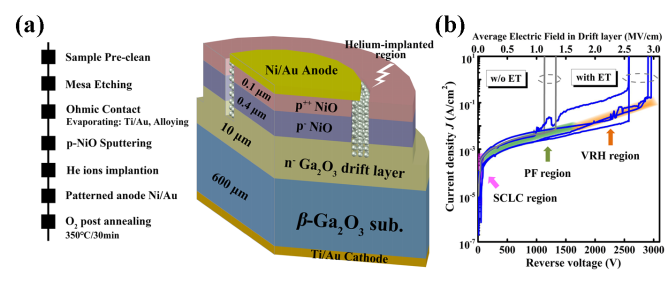

1. He离子注入终端实现3kV氧化镓功率二极管

本研究报道了一种高稳定性的垂直结构NiO/β-Ga2O3异质结二极管,该器件实现了3kV的高击穿电压和3.10 GW/cm²的巴利加优值。我们创新性地采用氦原子注入技术构建了高效低损伤的边缘终端结构,有效抑制了异质结PN结处的高电场聚集,将Ga2O3异质结二极管的击穿电压从1330 V提升至3000 V。通过拟合分析反向漏电机制,揭示了氦离子注入器件的独特击穿特性。进一步采用氧气退火工艺,将器件的比导通电阻从5.08 mΩ·cm2显著降低至2.90 mΩ·cm2,并提升了器件稳定性。研究成果以“3 kV/2.9 mΩ·cm2 β-Ga2O3 Vertical p–n Heterojunction Diodes with Helium-implanted Edge Termination and Oxygen Post Annealing”为题目发表在IEEE ISPSD 2025上并作现场口头汇报,第一作者为博士生韩甲俊。

图2.具有He离子注入终端的β-Ga2O3 HJDs(a)截面示意图和制造关键工艺,(b)反向击穿特性曲线。

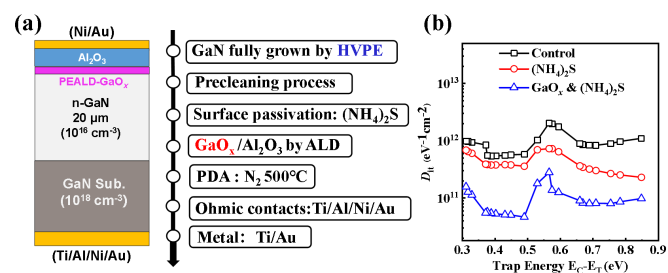

2. GaOx界面工程实现高性能氮化镓MOS电容器

在本研究中,我们采用氢化物气相外延技术,成功生长了低位错密度(~1.5×106 cm-2)的单晶氮化镓衬底及其外延层,这些材料被用于制造高质量的垂直氮化镓MOS电容器。我们引入了一种界面技术,通过等离子体增强原子层沉积在Al2O3/GaN界面处沉积一层薄薄的氧化镓作为中间层。实验结果显示,这些器件的界面陷阱密度(Dit)低至~8×1010 cm-2 eV-1,且VFB迟滞仅为50 mV。引入GaOx界面技术不仅有效抑制了栅极漏电流,还钝化了氮和氧相关的空位及悬挂键。这一方法为垂直氮化镓MOSFET的制造提供了新的方法。研究成果以“Enhancing Key Performance of Vertical GaN MOS Capacitors through GaOx Interface Technology”为题目发表在IEEE ISPSD 2025上,第一作者为硕士生林锦沛。

图3.具有GaOx界面层的垂直GaN MOS电容(a)结构示意图及关键工艺,(b)器件的界面态密度参数提取。

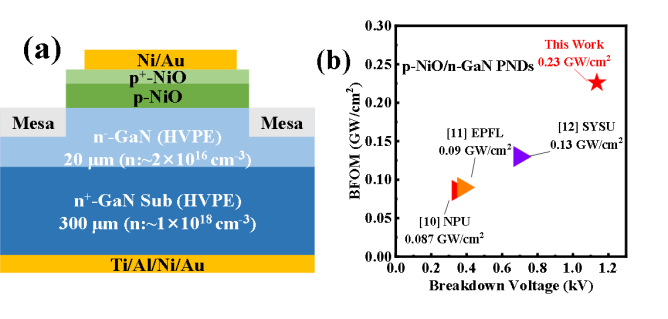

2. 高性能垂直p-NiO/n-GaN功率二极管

本研究报道了一种高性能的垂直p-NiO/n-GaN异质结二极管。通过氢化物气相外延技术生长的低位错密度氮化镓晶圆,N面经氧气等离子体处理(OPT)有效缓解了费米能级钉扎效应,并钝化了表面,使接触电阻(ρc)降至3.84×10-6Ω·cm2。通过氧气后退火处理溅射的氧化镍薄膜,优化了异质结界面。因此,击穿电压提升至1135 V,优值(FOM)达到0.23 GW/cm2,导通状态电阻降至5.7 mΩ·cm2。研究成果以“Enhancing Key Performance of Vertical p-NiO/n-GaN Heterojunction Diodes through Plasma Treatment and Oxygen Post-Annealing”为题目发表在IEEE ISPSD 2025上,硕士生黄烨莹、王敏为文章的共同第一作者。

图4.(a)NiO/GaN垂直pn HJD的结构示意图,(b)之前报道的NiO/GaN PND的FOM与击穿电压的对比。

以上研究成果得到了中国国家重点研发计划(2024YFE0205100)、广东省基础与应用基础研究重大专项(2023B0303000012)、广东省杰出青年科学基金(2022B1515020073)、深圳市科技计划(KJZD20240903102738050)以及深圳大学科学仪器开发项目(2024YQ003)的财政支持。