在近期落幕的第 37 届功率半导体器件与集成电路国际会议(IEEE ISPSD 2025)上,浙江大学电气工程学院电力电子器件实验室(PEDL)取得了令人瞩目的成绩。团队共有四篇论文被选为大会全体报告(Oral Session)。该核心报告数量在全球所有高校、研究机构和企业中位居第一,充分彰显了浙大 PEDL 团队在宽禁带功率半导体领域的卓越科研实力。

ISPSD 被誉为全球功率半导体领域的“奥林匹克盛会”,是该领域历史最悠久、影响力最大的顶级学术会议。本届会议于 2025 年 6 月 1 日至 5 日在日本熊本举行,汇聚了全球顶尖高校、科研院所及行业领军企业的核心研发力量。在这一国际顶尖学者云集的舞台上,浙大 PEDL 团队凭借其深厚的技术积淀和高水平的创新成果,赢得了与会专家的高度评价和广泛关注。

自2009年成立以来,PEDL团队长期聚焦宽禁带半导体器件的设计、制造与应用等核心方向。本次入选的成果覆盖了10kV 级碳化硅(SiC)MOSFET 芯片设计与批量制造、SiC 超级结(Super-Junction)功率器件、新型氧化镓(Ga2O3)功率器件以及先进封装等多个前沿方向,集中展现了团队在宽禁带半导体功率器件方向的系统性优势。此次的卓越表现,不仅是 PEDL 团队自身科研实力的有力证明,也标志着中国在功率半导体这一战略性科技领域的影响力正与日俱增。来自中国的创新声音,正在为全球功率半导体技术的发展注入新的活力与智慧。

图1.参会人员集体合照

本次入选的论文工作如下:

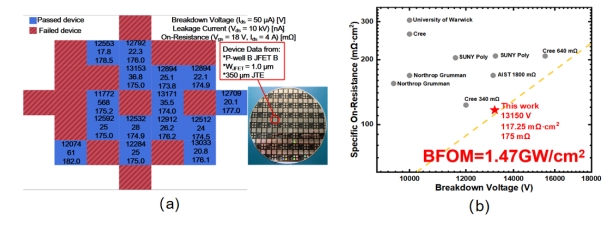

1. 高性能10kV-Rated SiC MOSFET器件

本项工作成功研制出10 kV电压等级,导通电阻175mΩ的SiC MOSFET器件。单芯片尺寸达到10mm × 10mm,击穿电压超过12kV,比导通电阻(Ron,sp)小于120mΩ·cm2 ,接近SiC材料的理论极限。为目前公开发表的最大尺寸、最低比导通电阻与最高通流能力的10kV等级SiC MOSFET芯片。通过设计与工艺的协同优化,所研制的万伏级芯片实现了超过50%的良率,具备批量制造的可行性,为后续的产业化推进与系统级应用奠定了坚实基础。

图2. (a) 10kV SiC MOSFET特性的整晶圆分布,(b) 本次成果与历史成果对比。

研究成果以“1 cm2 Chip Size, 10 kV Rated 4H-SiC MOSFETs with Efficient Termination Design and State-of-the-Art Device Performance”为题目发表在IEEE ISPSD 2025上并作现场口头汇报,第一作者为博士生孔令旭,通讯作者为任娜研究员。该成果不仅有望推动相关产业链的升级,同时有助于提升能源利用效率,促进绿色能源的普及应用,为社会的可持续发展贡献力量。

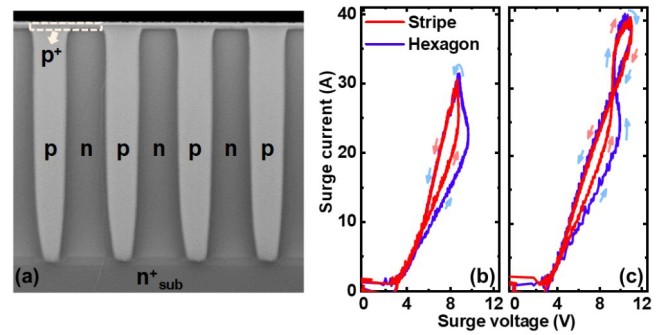

2. 碳化硅沟槽外延回填超级结二极管的双极型特性

本项工作采用深槽刻蚀和外延回填工艺,成功制备了3.3kV等级的4H-SiC超级结(Super-junction, SJ)二极管,表征了器件的静态I-V,变温C-V,双脉冲开关和浪涌电流特性,分析了超级结元胞类型以及不完全电离机制对器件浪涌特性的影响。器件最大浪涌电流密度达4000 A/cm²。还基于重复浪涌电流测试对比研究了SJ PiN和SJ SBD的浪涌可靠性差异。

图3. (a) 制备的超级结二极管截面SEM照片,(b) 30A和(c) 40A浪涌电流冲击下不同元胞类型器件的I-V轨迹。

研究成果以”Bipolar characteristics of 3.3kV-class 4H-SiC Epi-refilled Super-Junction Diodes”为题目发表在IEEE ISPSD2025上并作现场口头汇报,第一作者为博士生程浩远,通讯作者为王珩宇研究员。

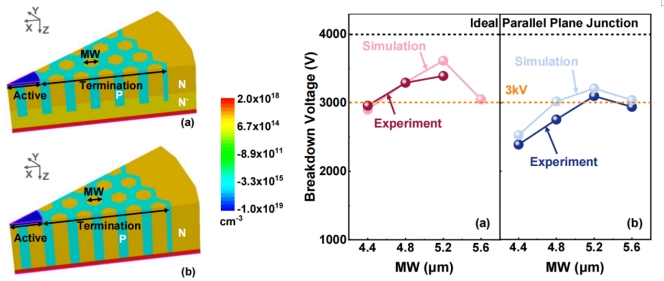

3. 3kV碳化硅半超结与全超结器件的电荷不平衡终端对比

本项工作使用深沟槽加外延回填技术路线,实现了3kV的碳化硅半超结及全超结SBD,该SBD终端区域通过超级结P区电荷调制实现耐压,被称为电荷不平衡终端(CI-SJTE)。CI-SJTE是一种工艺简便的终端结构,可以将终端区域的高电场从表面调制到体内,有利于器件的长期可靠性。分析了CJ-SJTE在半超结器件中具有更高耐压效率的原因。

图4. (a) CI-SJTE终端结构示意图,(b) 全超结与半超结CI-SJTE耐压效率对比

研究成果以”Comparative Study on Charge-Imbalance Super Junction Termination for 3kV 4H-SiC Full-SJ and Semi-SJ Devices”为题目发表在IEEE ISPSD 2025上并作现场口头汇报,第一作者为博士生张弛,通讯作者为王珩宇研究员。

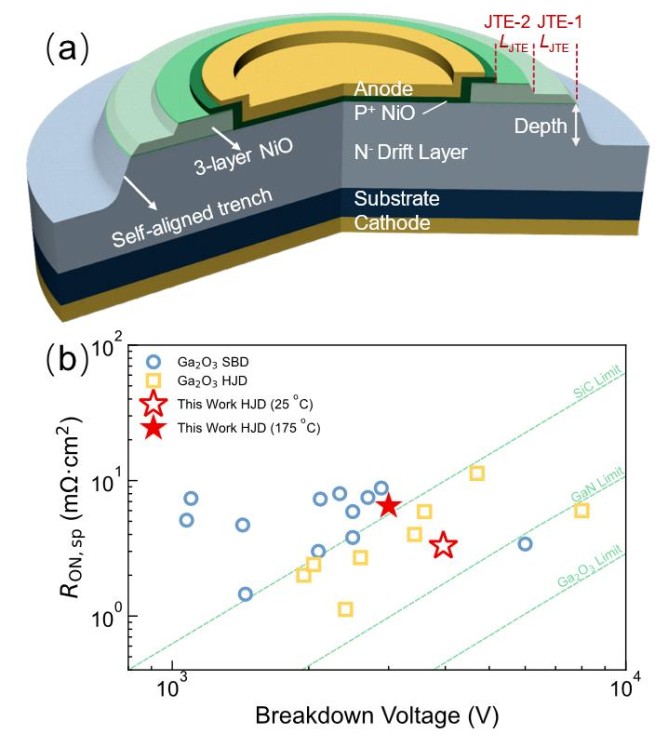

4. 具有高温工作能力的3.9kV垂直氧化镓异质结二极管

本研究展示一种新型垂直 β-氧化镓(β-Ga₂O₃)异质结二极管(HJD),采用自对齐多区结终端扩展(SA-MZJTE)技术,实现 3.9 kV击穿电压,比导通电阻 3.5 mΩ·cm2,功率品质因数 4.3 GW/cm2,且在 175 ℃高温下击穿电压超 3000 V,性能处于千伏级 Ga₂O₃二极管顶尖水平,表明 SA-MZJTE 是适用于中高压、高温 Ga₂O₃功率应用的高效终端解决方案。

图5. (a)器件结构示意图(b)本工作器件与其他器件的性能对比

研究成果以“3.9 kV Vertical β-Ga2O3 Hetero-Junction Diode With High-Temperature Operational Capability”为题目发表在IEEE ISPSD 2025上并作现场口头汇报,第一作者为博士生宛江彬,通讯作者为王珩宇研究员。

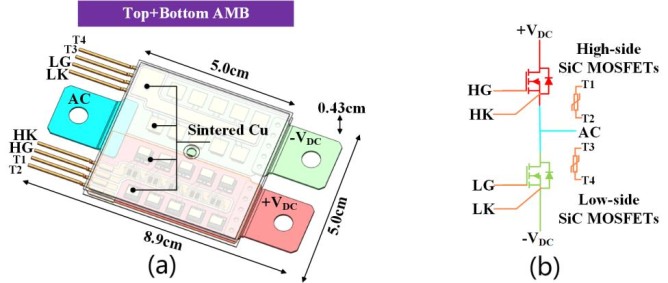

5. 基于低温无压铜烧结的大功率双面冷却SiC模块

本项工作开发了一种结构超紧凑、基于铜烧结的1200V 600A双面冷却SiC模块。模块体积仅为0.01075L,功率密度高达6.70×104 kW/L。测试结果表明,烧结铜接头的剪切强度高达43MPa,超过了MIL-STD-883 J标准的要求。此外,在额定工作电压1200V、额定工作电流600A的测试条件下,制造的DSC功率模块具有优异的开关特性。所提出的DSC功率模块总寄生电感仅为3.94nH,结到壳的热阻仅为0.112K/W。

图6. 提出的1200V 600A DSC SiC功率模块结构. (a) 铜烧结在DSC模块中的应用. (d) 模块的等效电路图.

研究成果以“A Novel High-Performance Double-Sided Cooling SiC Power Module based on Cu Sintering”为题目发表在IEEE ISPSD 2025上,第一作者为硕士生陈浩斌,通讯作者为闫海东研究员。