引言导读

近年来,随着半导体集成电路的微缩化,摩尔定律也逐渐接近极限,半导体集成电路对高密度集成工艺的需求变得更为迫切,键合技术已迅速发展成为了实现高密度互连和异质异构集成的不可或缺的核心工艺技术。目前,键合技术已经被广泛应用于集成电路半导体微电子学、电力电子学、光子学、生物医学、智能传感、光电集成、异质集成、3D集成以及先进封装等众多领域,并取得了重大研究进展。在未来,键合工艺技术的应用还将继续扩大。

本文是九峰山实验室发表在《化合物半导体》杂志上的文章节选,详细介绍键合工艺当前代表性技术与原理以及其在不同领域的典型应用,对实验室键合工艺能力展开详细介绍。

作者:张洁琼,柳俊,徐哲,熊伟,李成果,赵波,彭文斌,向诗力,王盼盼,邱磊,宋月平

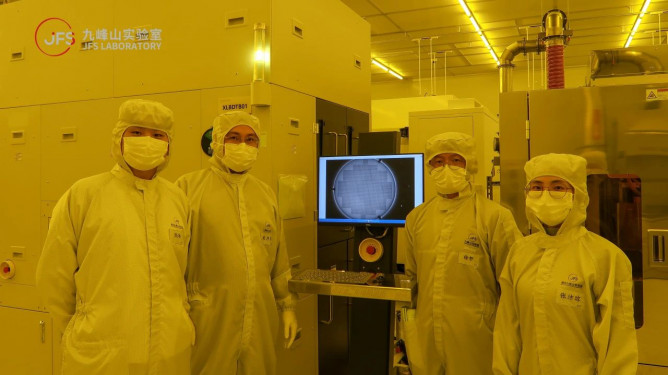

#团队介绍

九峰山实验室工艺中心键合工艺研发团队

九峰山实验室工艺中心聚集了全球优秀的技术研发团队和资深经验工艺工程师专家团队,专注解决产业共性关键工艺问题。键合工艺研发团队具备多种丰富键合工艺能力(如永久/临时键合、亲水/疏水键合、晶圆到晶圆键合、芯片到晶圆键合、熔融键合/金属热压/共晶键合等)及inline检测能力的异质晶圆键合平台,可实现多种化合物半导体材料的异质集成,具备先进的硅基光电子集成、MEMS圆片级封装等平台能力。团队陆续成功开发实现了具有超薄原子级的键合界面晶圆级异质键合技术、高良率高对准精度芯片-晶圆键合技术,以及低碎片率高效可靠的临时键合和解键合工艺方案等,并在实际产品如Si、lnP、GaN、SiC基器件晶圆的工艺流片中得到验证。

01

晶圆键合技术简介

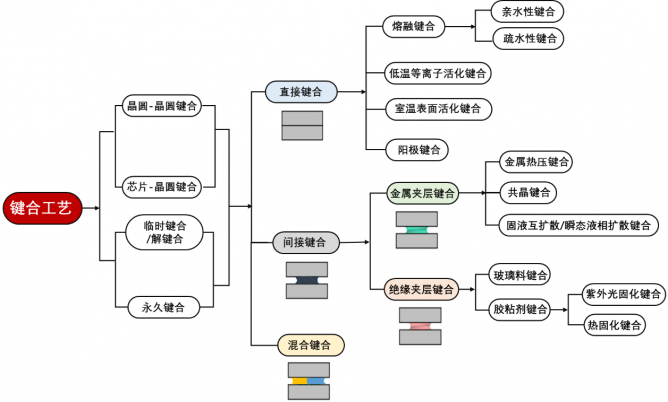

晶圆键合工艺技术是通过不同物理或化学的方法将两片表面光滑且洁净的晶圆紧密的贴合在一起,以辅助半导体制造工艺或者形成具有特定功能的异质复合晶圆。键合技术有很多种,通常根据晶圆的目标种类可划分为晶圆级(晶圆到晶圆)键合和芯片到晶圆键合。根据键合完成后是否需要解键合,又可分为临时键合和永久键合。根据待键合晶圆间是否引入辅助界面夹层,还可分为直接键合和间接键合。近年来,由于3D集成高密度互连及先进封装的迫切需求,还发展出一种新型的混合键合技术。

图1 主流晶圆键合技术的分类。

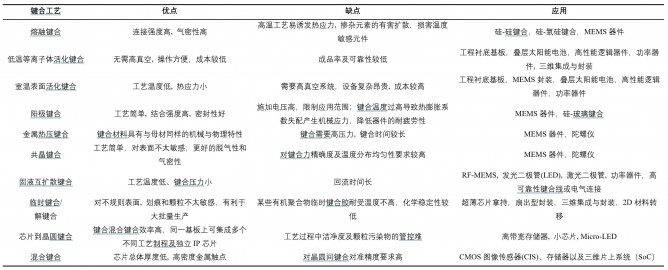

表1 各种类型键合技术的优缺点与典型应用总结

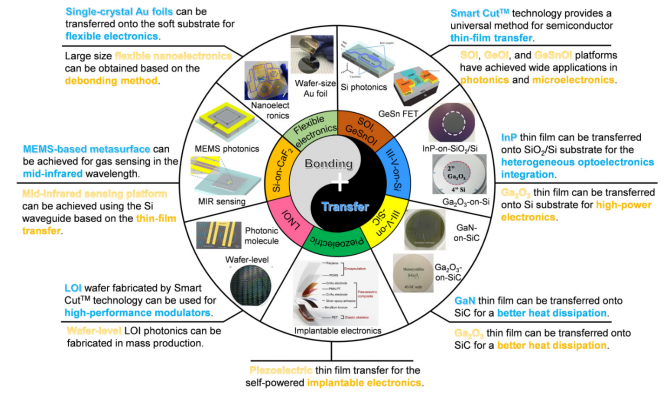

目前,键合技术已经被广泛应用于集成电路半导体微电子学、电力电子学、光子学、生物医学、智能传感、光电集成、异质集成、3D集成以及先进封装等众多领域,并取得了重大研究进展。在未来,键合工艺技术的应用还将继续扩大。

图2 键合及转移技术的广泛应用(图片来源:Z. Ren et al., Micromachines, vol. 12, no. 8, p. 946, 2021)

02

键合技术典型应用

超薄器件晶圆的制备

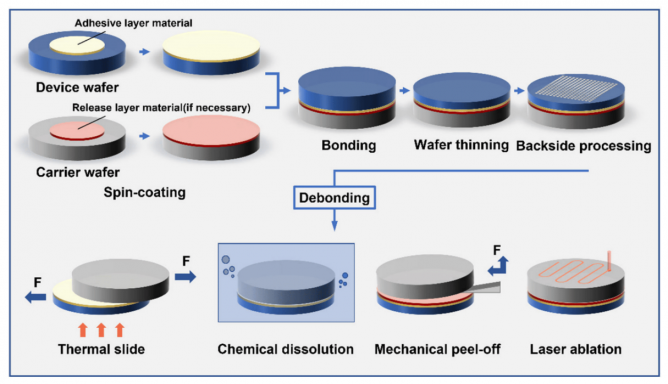

随着半导体元器件的不断小型化和集成化,对于超薄晶圆(厚度小于100 μm)的需求变得愈发显著。对于超薄器件晶圆尤其是化合物半导体材料晶圆,由于其自身柔性和易脆性以及在前道加工过程中容易出现翘曲、起伏和封装精度低等问题,导致其在后续工艺加工过程中容易受损,且物理结构和稳定性发生严重恶化。研发人员提出了一种解决方法,即通过采用一个载体晶圆(通常用硅、玻璃或蓝宝石衬底)作为临时支撑系统,通过粘合剂与超薄器件晶圆暂时性地粘结在一起,以便顺利进行后续加工。当后续工艺全部完成后,再将临时支撑的载体晶圆与超薄器件晶圆分离。临时键合/解键合工艺技术应运而生。随着先进封装技术与3D集成的飞速发展,如今此技术已发展成为面向大尺寸超薄晶圆的拿持与后道工艺加工处理的重要解决方案

近年来,激光解键合技术因其具备能量输入效率高、器件损伤低以及操作灵活等优点,更容易满足低损耗、高效率、大规模制造的需求,更适用于大尺寸超薄晶圆以及特殊易脆材质晶圆如化合物半导体材料晶圆,极具广阔应用前景。

图3 临时键合/解键合技术工艺流程示意图(图片来源:Z. Mo et al., Electronics, vol. 12, no. 7, p. 1666, 2023)

多功能复合衬底的制备

随着传统硅器件尺寸接近极限,将晶体管进一步缩小至纳米尺度变得愈发困难。为了应对信号串扰和元素扩散等问题,SOI绝缘体上晶圆作为传统硅衬底的替代方案受到重点关注。智能剥离(Smart CutTM)技术,又被称为衬底行业的“纳米刀”,最早由SOITEC与CEA-LETI联合开发,并结合晶圆键合工艺进而开发了如今广泛应用于业界的SOI晶圆制备技术。晶圆直接键合技术与该技术结合,可克服不同晶格材料限制,因而使得许多单晶薄膜可转移到其他衬底上。为多功能复合衬底制备和多功能材料间的异质集成提供新可能。

三维集成与封装

近年来,键合工艺技术已经成功地应用于存储器堆叠、计算与通信系统中的存储器/微处理器堆叠, 2.5D/3D集成以及先进封装等众多领域中。基于混合键合的3D集成封装技术,通过TSV互连将芯片垂直堆叠,可以实现微米级以下间距的高密度集成,缩短了传输路径,提高了整体芯片的速度和性能,已广泛应用于高带宽存储器与CPU、GPU、及FPGA等处理器的芯片整合。然而,混合键合工艺中仍存在一些技术挑战,例如亚微米级以下高对准精度的要求,以及洁净度和缺陷管控等问题,仍有待后续更多的测试与持续的工艺验证,以实现最终优化与提高。

光电集成

随着全球数据需求的指数级增长,光子集成芯片以光子为信息传输媒介,因具有高带宽、高速率、高灵敏度等优点,已广泛应用于光通信、光互联、光学传感等领域。由于CMOS工艺制造的兼容性,电子学和光子学可以集成在同一芯片中。硅上激光源的集成是硅基光子学的关键挑战。基于晶圆级键合及芯片到晶圆键合技术实现异质异构集成,被认为是更有利的光子集成芯片的制备方法。然而,根据材料不同,制备工艺也有很大的区别,因此要确保引入的工艺的兼容性。

03

九峰山实验室键合工艺平台

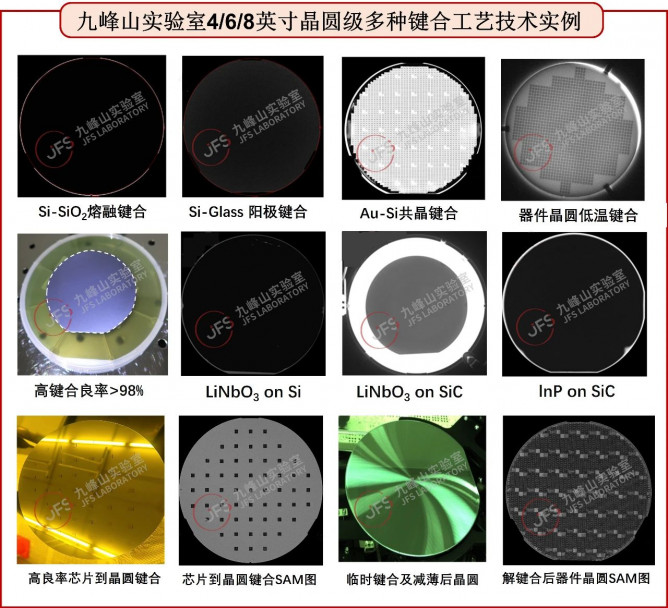

九峰山实验室已建设完成先进的键合工艺平台,拥有全球顶尖的多种类型键合设备,如全自动熔融键合设备、超高真空室温键合设备、高压键合设备、芯片-晶圆键合设备、临时键合/解键合及清洗设备等,可提供支持多种键合工艺能力与开发及加工服务,包括永久/临时键合、亲水/疏水键合、混合/熔融键合,阳极键合、金属热压键合、共晶键合及瞬态液相键合等,同时满足可兼容4/6/8英寸的硅基及化合物半导体材料衬底的晶圆级晶圆到晶圆键合和芯片到晶圆键合,以满足异质异构集成的需求。同时,配合先进的inline键合量测设备和全面的前后道工艺,以及强大的检测分析平台能力,九峰山实验室可为合作伙伴提供多材料、多结构、多功能、多体系、多元化的异质异构集成的解决方案,支撑硅基光电融合、MEMS制造与真空封装、功率及无线器件制造、3D集成与先进封装、Chiplet、生物芯片、AI互联网等相关领域的创新研究与开发工作。

图4 九峰山实验室晶圆级键合工艺技术实例

针对键合工艺中高温引发的异质材料间热应力和晶圆形变问题,九峰山实验室成功研发出多种材料间的室温直接键合工艺,极大地降低了异质材料间的热应力和晶圆形变,使得大尺寸异质材料晶圆间具备超薄原子级界面的高强度键合成为可能。为实现低成本的硅基光电子芯片融合,实验室键合技术团队通过高对准精度芯片-晶圆键合技术,成功实现了8寸Si晶圆上InP芯片的高良率键合。此外,为满足微纳器件制造及MEMS晶圆级封装应用需求,针对化合物半导体晶圆易碎问题,开发出一套高效可靠的键合和解键合工艺方案,成功地降低了大尺寸化合物半导体薄片晶圆的碎片率,极大地提高了后续工艺良率,已经在实际产品如Si、lnP、GaN、SiC基器件晶圆的工艺流片中得到了初步验证。

随着芯片平面微缩工艺已接近极限,进一步提高芯片密度和性能必然需向三维方向、面向多种材料进行集成。未来,九峰山实验室键合异质集成平台将继续围绕异质异构集成、先进封装、先进复合材料等技术领域,持续进行技术创新,突破技术瓶颈,不断丰富和增强工艺能力,为全球合作伙伴提供更优质的服务。