台积电、三星、英特尔等芯片大厂近期积极布局背面供电网络(BSPDN),像三星计划将BSPDN技术用于2纳米芯片,该公司近日也于日本VLSI研讨会上公布BSPDN研究结果。

根据比利时微电子研究中心(imec)的说法,BSPDN目标是减缓逻辑芯片正面在后段制程面临的壅塞问题,通过设计技术协同优化(DTCO),在标准单元实现更有效率的导线设计,协助缩小逻辑标准单元的尺寸。

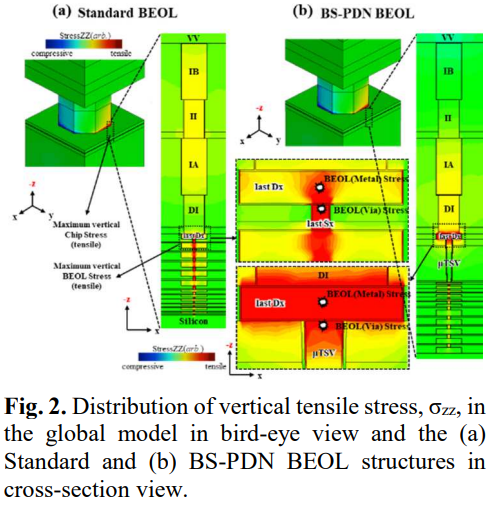

BSPDN 可解释成小芯片设计演变,原本将逻辑电路和存储器模组整合的现有方案,改成正面具备逻辑运算功能,背面供电或讯号传递。

一般而言,通过晶圆正面供电的方法虽能完成任务,但会使功率密度下降、性能受损。

三星称跟传统方法相比,BSPDN可将面积减少14.8%,芯片能拥有更多空间,公司可增加更多晶体管,提高整体性能; 线长也减少9.2%,有助降低电阻、使更多电流通过,进而降低功耗,改善功率传输状况。

▲ 三星分享 BSPDN 研究成果 (Source:三星)

今年6月,英特尔也举办了BSPDN相关的发布会,并将其命名为PowerVia。该公司计划在英特尔20A制程中采用这方法,使得芯片利用率有望达到90%。

英特尔认为,PowerVia将解决硅架构中的互连瓶颈,透过晶圆背面提电来实现连续传输; 该公司预计在2024年推出的 Arrow Lake CPU 中采用这种新方法。

另有消息称,台积电如期2025年上线2纳米制程,2025年下半年在新竹量产,计划2026年推出N2P制程,这个制程将采用BSPDN技术。

来源:科技新报