近日,被业界誉为“芯片设计国际奥林匹克”的第70届国际固态电路大会(ISSCC 2023)在美国旧金山举行,东大电子科学与工程学院/集成电路学院的师生赴美参加此次盛会三项重大研究成果入选。

此次会议是自2020年以来首次全线下模式召开,来自30多个国家的3000多名研究人员参会,分享该领域的最新技术。约有200项芯片实测成果入选,约45%的芯片成果来自于英特尔、三星、台积电、AMD、英伟达、高通、博通、ADI、TI、联发科等国际芯片巨头公司,其余芯片成果来自于高校和科研院所。

东南大学电子科学与工程学院/集成电路学院的师生赴美参加此次盛会,国家ASIC工程中心杨军教授、司鑫副研究员和蔡浩副教授课题组,在存储器领域的Session 7和Session 33报告了三项存内计算芯片研究成果,是本届ISSCC在存储器-存内计算领域报道数量最多的单位之一。同时,东南大学作为IEEE固态电路南京分会主席单位,派出代表参与本年度IEEE固态电路协会主席论坛。

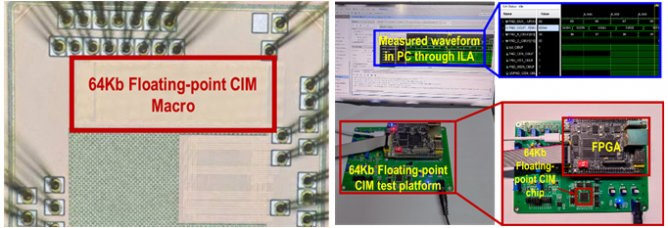

浮点存内计算芯片

面向高精度AI运算场景,针对整型神经网络在复杂任务下性能大幅下降的问题,东南大学团队提出一套基于共享指数的浮点存算架构,通过片外权重指数域对指,片上指数相加对指,全局浮点局部定点的方式,实现浮点运算。同时设计了一套高位全精度、低位近似的数字运算架构,以分离字线方式实现了数字域的高能效运算。通过对数字域存算的加法树结构进行分解,权重、特征值、通道三段加法树的重组实现计算效率的提升。

该工作以《A 28-nm 64-kb 31.6-TFLOPS/W Digital-Domain Floating-Point-Computing-Unit and Double-Bit 6T-SRAM Computing-in-Memory Macro for Floating-Point CNNs》为题,文章第一作者为东南大学集成电路学院博士生郭安。

边缘端网络存内计算芯片

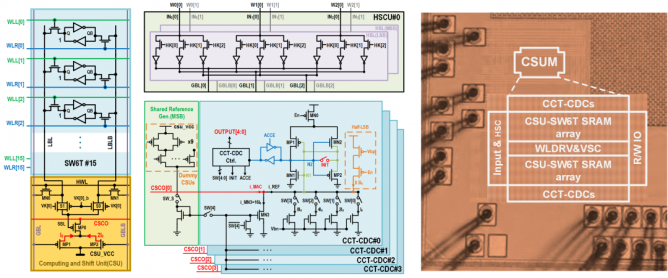

面向Edge端神经网路的加速任务,传统的存内计算设计面临诸多问题和挑战,主要包括短累加致能效下降、阵列利用率低,数据更新成本高和计算-读出访问时间过长等。东南大学团队提出一种用于Edge端神经网络加速的存内计算芯片设计。架构层面,首次提出一种灵活可配置的存算一体阵列,支持两种数据映射方式,在提高阵列利用率的同时可极大降低数据更新成本。

该工作以《A 28-nm Horizontal-Weight-Shift and Vertical-Feature-Shift based Separate-WL 6T-SRAM Computation-in-Memory Unit-Macro for Edge Depthwise Neural-Networks》为题,文章第一作者为东南大学集成电路学院的博士生王博。

自旋转移力矩磁随机存储器(STT-MRAM)存内计算芯片

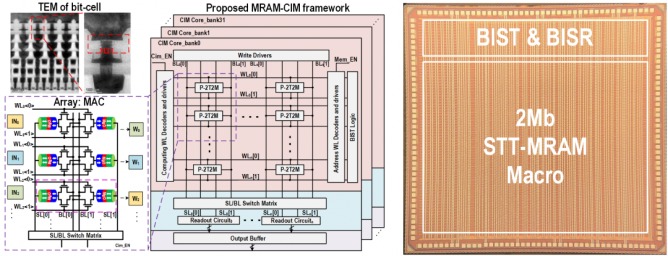

该工作面向资源受限的边缘人工智能设备,解决了新型非易失磁存储器STT-MRAM存算电路自下而上设计中的挑战。东南大学团队研制了一款28nm 2Mb的高能效STT-MRAM存内计算芯片,在1-bit输入/1-bit权重/9次累加/5-bit输出的情况下,实现了高达41.5 TOPS/W的峰值能效,以及96.2%(MNIST数据集)的网络推理精度,是中国大陆首篇在ISSCC上发表的MRAM存储与存算工作。

该工作以《A 28nm 2Mb STT-MRAM Computing-in-Memory Macro with a Refined Bit-Cell and 22.4 – 41.5 TOPS/W for AI Inference》为题,文章第一作者为东南大学集成电路学院蔡浩副教授。

据悉,ISSCC是由电气与电子工程协会(IEEE)固态电路学会赞助发起的半导体集成电路设计领域的学术会议,该会议于1954年首次举办,是该领域规模最大、最著名的国际会议。历史上入选ISSCC的成果代表着当年度全球领先水平,展现出芯片技术和产业的发展趋势,多项“芯片领域里程碑式发明”在ISSCC首次披露,如世界上第一个集成模拟放大器芯片(1968年)、第一个8位微处理器芯片(1974年)和32位微处理器芯片(1981年)、第一个1Gb内存DRAM芯片(1995年)、第一个多核处理器芯片(2005年)等。

(来源:东南大学)