氧化镓(Ga2O3)半导体具有4.85 eV的超宽带隙、高的击穿场强、可低成本制作大尺寸衬底等突出优点。有望实现更高耐压、更低损耗、更高效率。可以通过熔融法制备低成本、大尺寸单晶衬底。氧化镓半导体在大功率器件、日盲紫外光电探测应用方面受到极大关注。

近期,在西安召开的“2023功率与光电半导体器件设计及集成应用论坛”上,厦门大学教授张洪良带来了”宽禁带氧化镓薄膜外延及电子结构研究”的主题报告,报告介绍了氧化镓材料发展现状,并重点介绍了其课题组在氧化镓薄膜外延、掺杂与缺陷机制以及表界面电子结构等方面的研究进展。

当前,鉴于广阔的发展前景,氧化镓材料和器件已成为世界科技前沿和国家战略竞争要地。比如日本经济产业省(METI) 近五年投资超过1亿美元,支持氧化镓半导体材料开发。美国国防部/空军实验室联合Cornell/UCSB和企业在2012年建立了氧化镓材料与器件研究部门。德国莱布尼茨晶体生长研究所(IKZ)2009年开始研发Ga2O3 晶体,实现4英寸的晶体,为美国空军实验室供应外延基片。

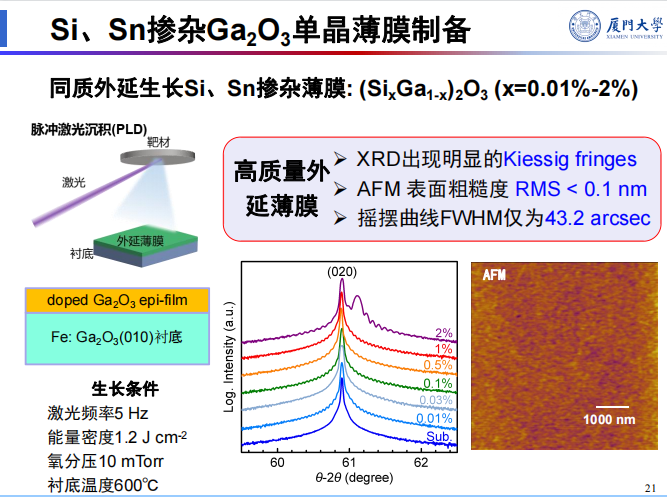

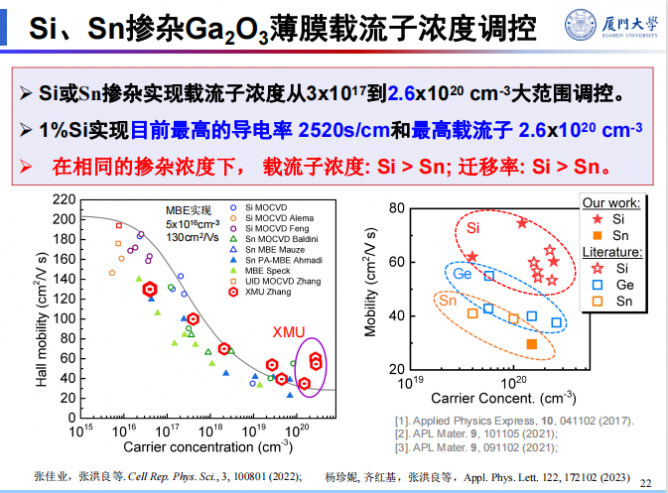

从氧化镓半导体产业链来看,单晶衬底和外延薄膜是功率和光电器件的关键材料基础,其品质直接决定器件性能。高品质氧化镓外延薄膜以及缺陷与掺杂调控是器件应用的关键。目前国外已实现导模法4英寸单晶初步量产,6英寸晶坯的突破。国内已逐步实现4英寸晶体。氧化镓薄膜外延进展方面,采用MOCVD、MBE、HVPE等技术外延生长氧化镓薄膜。通过Si、Sn等掺杂实现载流子浓度从1015到1020 cm-3范围的调控。对于氧化镓薄膜外延存在的问题,报告认为大部分外延研究工作集中在(010)面衬底;然而(100), (001) 面更容易获得大尺寸衬底,但缺陷,位错密度高,生长速度慢。需进一步发展低背景载流子浓度、低缺陷密度的外延薄膜等。

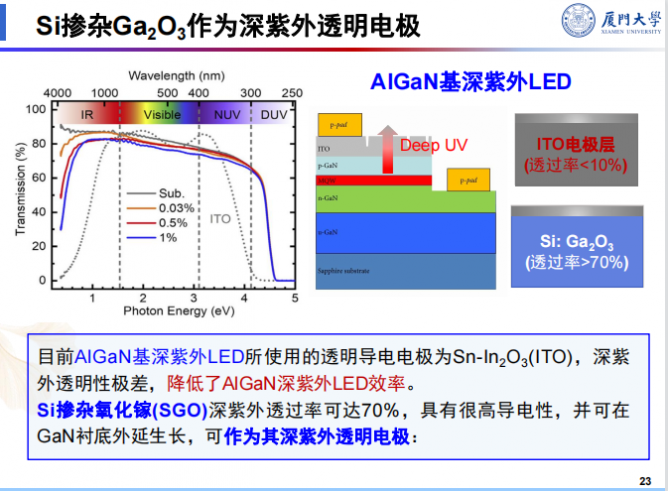

报告介绍了设备与表征技术,以及Si、Sn掺杂氧化镓电子结构研究成果,研究利用脉冲激光沉积和分子束外延技术分别通过Si和Sn掺杂实现了氧化镓外延薄膜载流子从3×1017 cm-3到 2.6×1020 cm-3的大范围调控。其中,1% Si掺杂的Ga2O3薄膜实现了目前文献报道的最高导电率 2520 S/cm和最高载流子浓度 2.6×1020 cm-3。结合同步辐射硬X射线光电子能谱(HAXPES)和密度泛函理论(DFT)计算,阐明了Si是氧化镓最优选的n型掺杂剂,并提出Si共振掺杂机制的理论模型。明晰缺陷与掺杂机制,极少量杂质/缺陷的抑制策略。

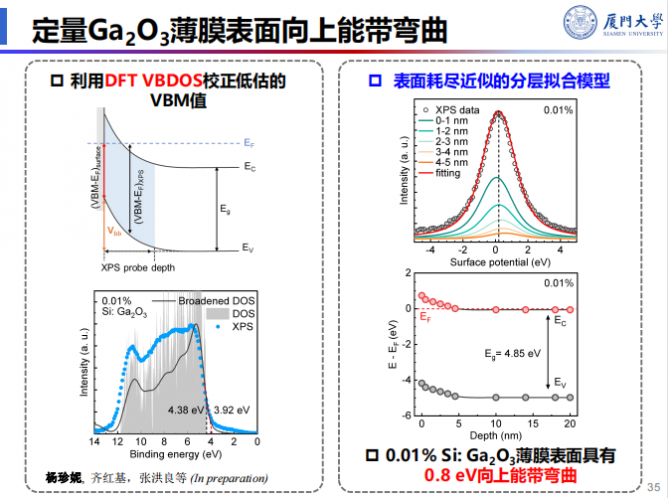

另一方面,课题组也对氧化镓薄膜的表界面电子结构进行系统研究,发现氧化镓表面存在高达0.8 eV的向上能带弯曲,其内在原因是Ga 4s轨道构成的导带底部能量较高和氧化镓较低的功函数(仅为3.2 eV)。向上的能带弯曲给Ga2O3欧姆接触带来挑战。Si重掺杂的氧化镓薄膜能有效缓解肖特基势垒的形成。

研究在氧化镓薄膜外延、缺陷与掺杂机制和表界面电子结构的研究结果为氧化镓材料和光电子器件的开发具有一定的指导意义。

论坛相关信息

本次CASICON系列活动之“2023功率与光电半导体器件设计及集成应用论坛(西安站)”由第三代半导体产业技术创新战略联盟(CASA)指导,西安交通大学、极智半导体产业网(www.casmita.com)、第三代半导体产业主办,西安电子科技大学、中国科学院半导体研究所、第三代半导体产业技术创新战略联盟人才发展委员会、全国半导体应用产教融合(东莞)职业教育集团联合组织、西安和其光电股份有限公司等单位协办。

CASICON 系列活动简介

“先进半导体产业大会(CASICON)”由【极智半导体产业网】主办,每年在全国巡回举办的行业综合活动。活动聚焦先进半导体产业发展热点,聚合产业相关各方诉求,通过“主题会议+项目路演+展览”的形式,促进参与各方交流合作,积极推动产业发展。CASICON 系列活动将以助力第三代半导体产业为己任,联合实力资源,持续输出高质量的活动内容,搭建更好的交流平台,为产业发展贡献应尽的力量。

(备注:以上信息仅根据现场整理未经嘉宾本人确认,仅供参考!)