碳化硅MOSFET在大功率开关应用中的卓越性能使其在一些关键增长领域得到广泛使用,例如工业电机驱动器的控制。在此应用中,功率半导体器件的关键性能指标之一是其短路(SC)耐受能力。电机驱动器运行的恶劣环境可能导致故障情况(如逆变器击穿事件和电机绕组中的绝缘击穿)下过流。因此,SC功能是器件制造商对其零件执行的可靠性测试之一。该测试是独一无二的,因为当栅极脉冲打开时,器件在特定应力间隔内承受高电压和高电流。

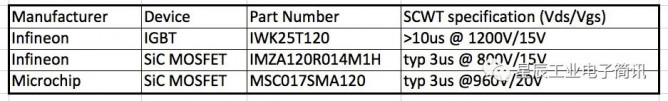

俄亥俄州立大学的Agarwal教授和他的团队一直处于对SiC器件的各个方面进行可靠性研究的最前沿。1–5在本文中,我们将回顾他们工作的一些发现,并重点介绍各个小组在SC能力方面的一些改进。短路耐受时间(SCWT)是衡量器件承受SC能力的关键指标,传统上用于此类应用的硅IGBT具有出色的SCWT,如表1所示。

表1:比较Si IGBT和SiC MOSFET的SCWT规格,额定电压均为1,200V

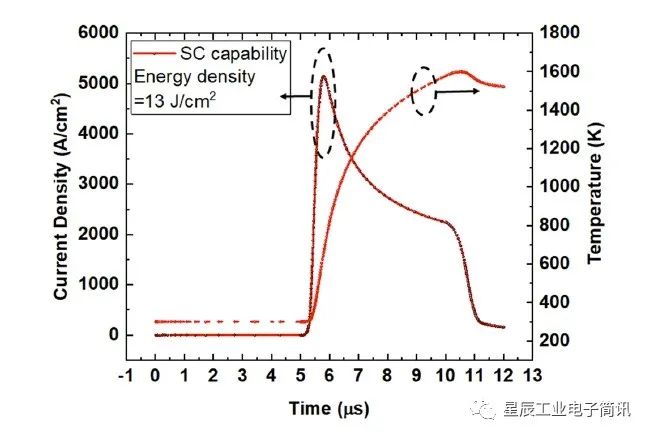

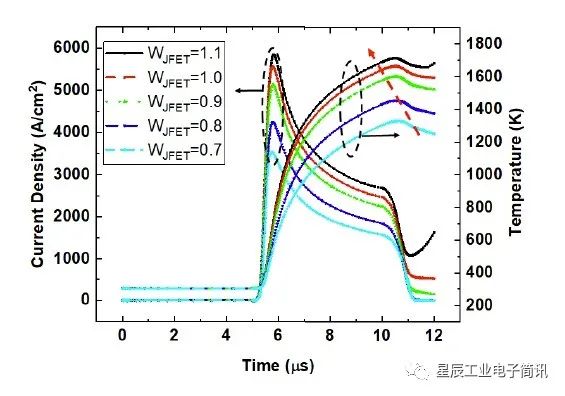

对SiC MOSFET中SC事件的响应如图1所示。这些来自1.2kV碳化硅MOSFET的仿真显示SC事件导致的高电流和温度。

图1:SC事件的仿真结果 — 显示SiC MOSFET的电流和芯片温度

限制碳化硅场效应晶体管SCWT的因素

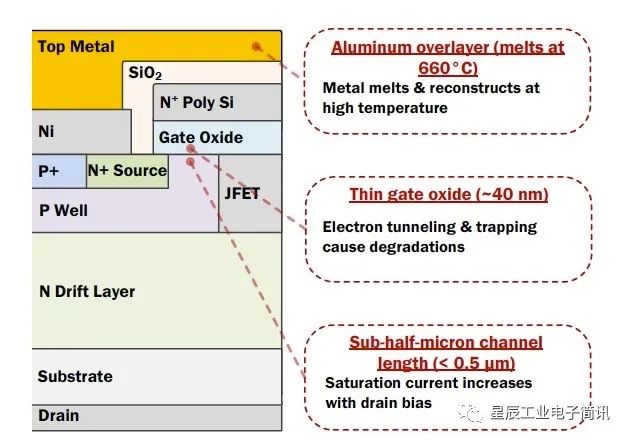

图2显示了SiC平面VDMOS器件的横截面。如图所示,该设备中已确定三个弱点。5该器件的顶部金属通常是铝,其熔点为660°C。SC事件期间的高功率密度可能导致温度超过此温度。铝可以通过下方钝化层中的晶界熔化和扩散,从而可能造成灾难性的器件损坏。

由于界面状态阱,SiC中的反转通道迁移率远低于Si,因此SiC中使用的栅极氧化物厚度(通常为40-50 nm)远低于Si中用于类似栅源电压的100 nm(VGS)评级。因此,在最大漏源电压(VDS)条件下可能在栅氧化层上产生隧道,这反过来又会导致氧化物中的电荷被捕获并改变器件阈值电压(Vth)。更高的导通状态器件电阻(RDS(on))的结果也可能导致器件温度升高的正反馈。这将增加SC电流。

SiC MOSFET中的沟道长(Lch)通常在0.5μm或更低,远小于功率Si MOSFET中沟常使用的1μm左右。这也是为了补偿较低的沟道迁移率。短Lch可产生高输出电导和饱和电流(Idsat),因为在高VDS时漏极引起的屏障降低,从而产生更高的功率耗散和更低的SCWT。

图2:显示薄弱区域的SiC平面栅MOSFET横截面5

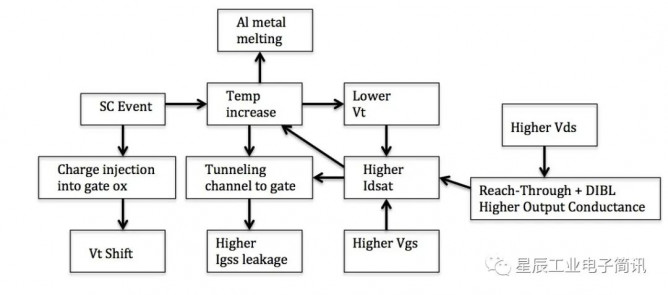

图3显示了来自SC事件的器件内的事件流。很明显,降低器件Idsat随之而来的温度升高将是提高其承受此类事件的鲁棒性的关键。

图3:SC事件流

提高SC鲁棒性的方法

沟道长度(Lch)、JFET宽度(Wjfet)、栅氧化层厚度(Tox)、漂移层厚度

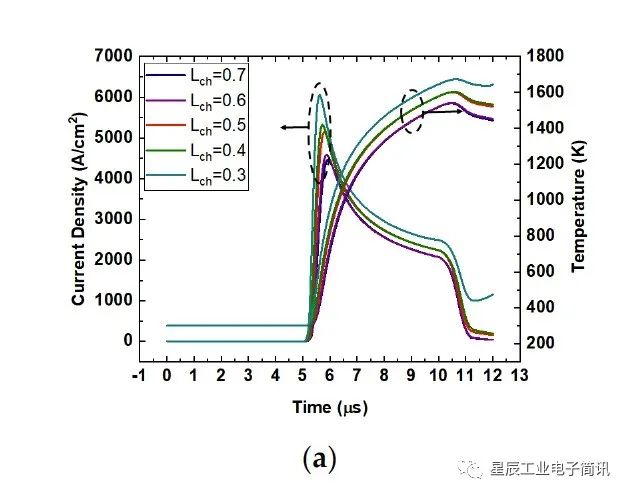

增加沟道长度Lch,减小Wjfet,并增加Tox可以降低器件IDSAT。对Lch和Wjfet变化的响应模拟1,6如图4所示。Wjfet变化对SC电流有显著影响。较厚的Tox还将使栅极对源极到栅极的漏电流(IGSS)具备更好的鲁棒性。较厚的漂移区有助于器件的热容,并降低高VDS偏置下直通的可能性。不幸的是,所有这些变化也会增加器件的RDS(on)。

图4:通过TCAD仿真的SC事件电流密度和温度vs(a)Lch和(b)1/2 WJFET6的关系

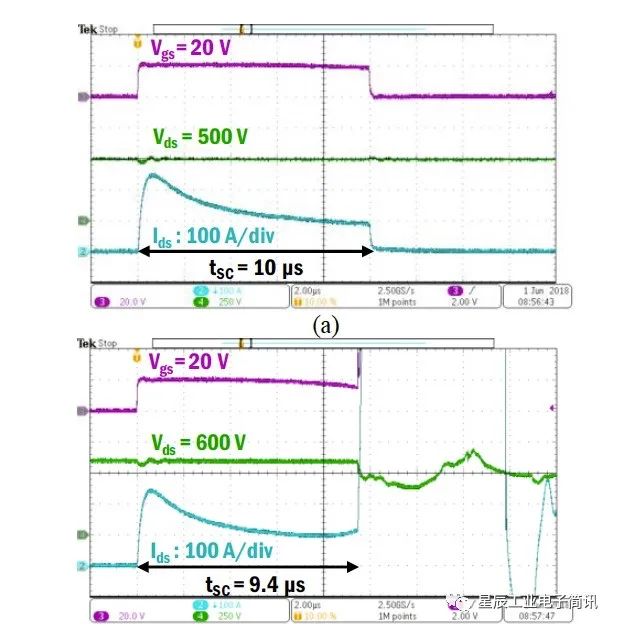

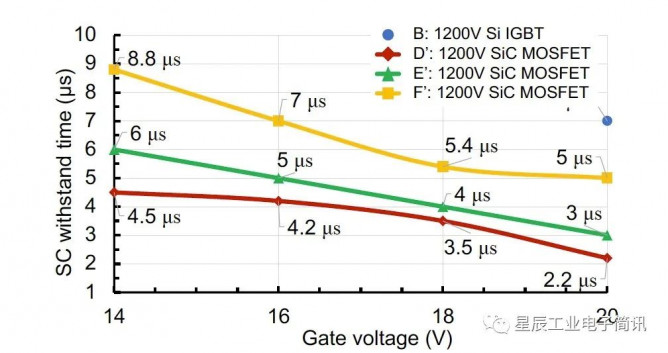

Vds,Vgs不同设置下的电压降额

更高的Vds或更高的Vgs减少器件SCWT5,分别如图5(a)和5(b)所示。这些图是根据不同器件制造商的1200V SiC MOSFET进行SC测量获得的(如图5(b)中显示为D、E和F)。在Vgs为20V下的Vds响应也显示了在较高Vds下Vgs随时间变化的波形,展示了Igss漏电流。图5(b)展示了在Vds为800V时的1200V Si IGBT器件数据作为比较。其降额的缺点是增加了RDS(on)或芯片面积。

一项有趣的研究7发现当负Vgs用于关断时,与采用0V时相比,SCWT改善了10%至20%。认为负栅极驱动器增加的电感有助于降低峰值SC电流。

图5:(a)SCWT vs. Vds;(b)SCWT vs. Vgs

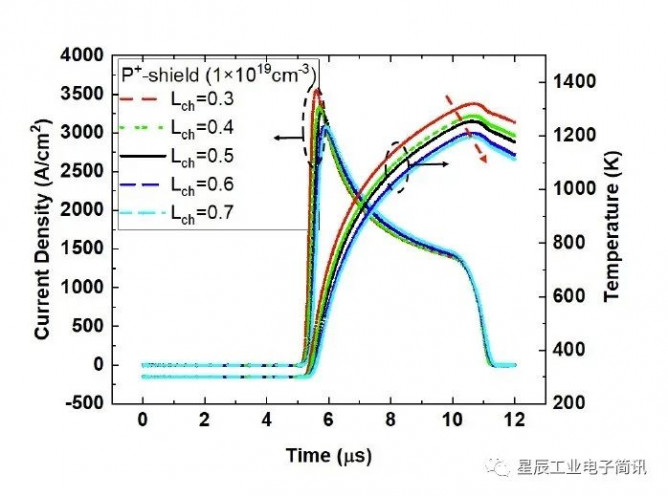

在P阱下使用P+屏蔽区

在图1所示的P阱下植入P区域将有助于限制高Vds偏置下的漏极电压穿透,有效屏蔽器件的JFET区域并降低IDSAT电流6,8。图6显示了沟道Lch变化时的仿真结果,类似于图4中使用的仿真,但包含P+屏蔽。比较图4和图6之间的数据,屏蔽降低了IDSAT电流并增加SCWT。这种方法的优点是RDS(on)不受到影响。

图6:带P+屏蔽区时,器件SC电流密度与沟道长度Lch的关系

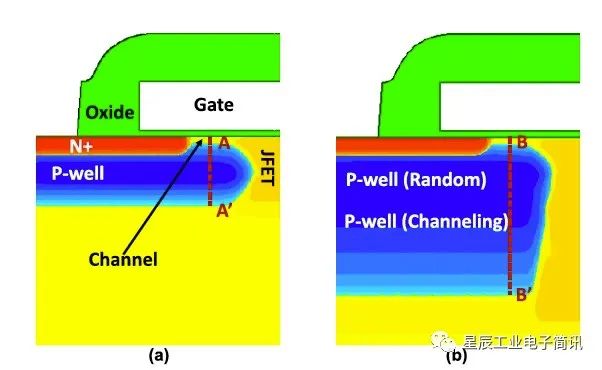

阱的工艺影响

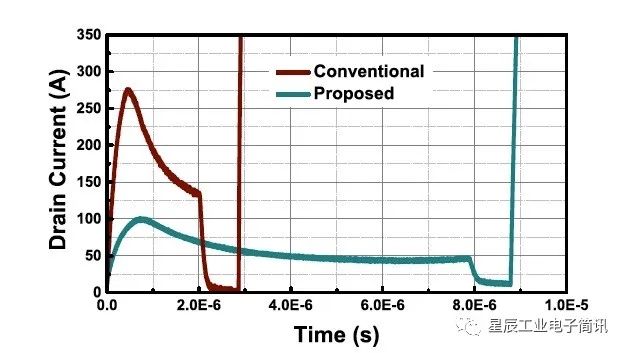

使用更深的P阱作为准场板,降低JFET区域栅极氧化物界面处的电场,并抑制高Vds下的沟道泄漏电流。使用倾斜4°的沟道植入物来实现这一目标的新方法产生了非常有希望的结果9,不仅改善静态特性,而且即使采用短Lch也能实现高Vds击穿电压和沟道泄漏电流,同时也在SCWT范围内。图7说明了更深的P阱的概念,图8显示了实现的SCWT改进。一个显着的优点是RDS(on)的变化非常少,如图所示,SCWT显著提高~4×至8μs。

图7:显示常规阱和新的沟道阱剖面图9

图8:1200V碳化硅沟槽式场效应管MOSFET在Vgs为20V,Vds为800V时沟道更深阱的SC响应9。

在沟槽SiC MOSFET中,栅极不太可能暴露在最大电场下。因此,SCWT优于平面MOSFET。研究7显示SC承受能量(在SC事件发生时间段内的∫VDS×IDS),对于额定值与平面器件相似的沟槽FET,其高出约50%。此外,基本沟槽结构的改进可以产生更小的RDS(on),同时降低IDSAT电流以及改进SCWT。ROHM新推出的第四代SiC双沟槽MOSFET就是一个例子。10

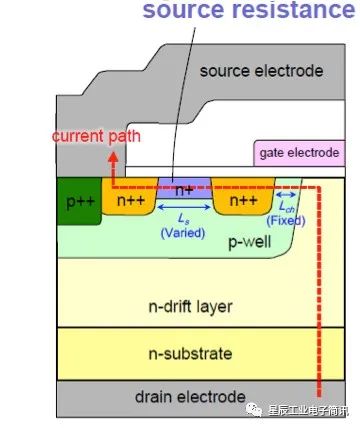

嵌入式源极电阻

通过用额外的嵌入式源极电阻(Rs),如图9所示,11已经证明,具有Rs区域不仅可以在短路时具有高电阻,而且在实际温度范围内也可以具有低电阻。在源极结和顶部铝金属之间使用具有强正温度系数的金属也有助于限制IDSAT随温度的上升。

图9:带Rs的SiC MOSFET横截面示意图11

已经证明了其它几种基于电路的方法来改善SCWT,这里不再讨论。此外,栅极驱动器必须与MOSFET协同工作,以确保驱动器在MOSFET的规格限值内关断。因此,快速检测将是栅极驱动器开发工作的关键部分。

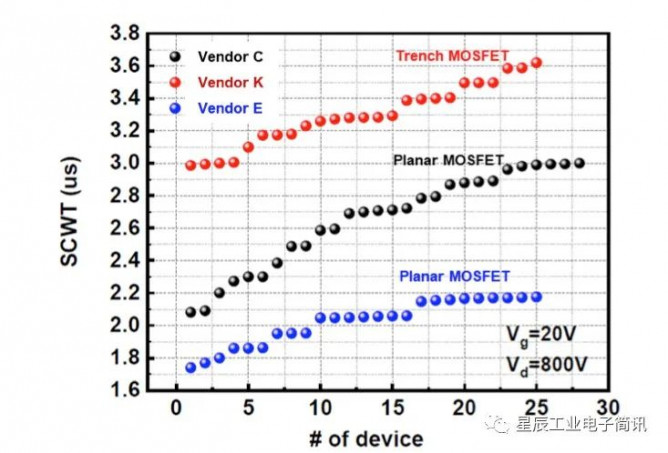

给定供应商的SCWT变化

来自不同供应商的商用SiC MOSFET的SCWT已经过俄亥俄州立大学Agarwal教授小组的测试。对于每个供应商,测试了多个器件。每个供应商的SCWT变化如图10所示。对于给定的供应商,观察到显著的SCWT差异。最有可能的是,SCWT的这些变化是由于沟道长度和JFET宽度的工艺相关变化造成的。

图10:来自不同供应商的商用SiC MOSFET的SCWT测量

参考文献:

1.Maddi et al. (2021). “The Road to a Robust and Affordable SiC Power MOSFET Technology.” Energies 2021.

2.Liu et al. (2020). “Gate oxide reliability studies of commercial 1.2 kV 4H-SiC power MOSFETs.” IEEE International Reliability Physics Symposium (IRPS).

3.Xing et al. (2019). “Current saturation characteristics and single-pulse short-circuit tests of commercial SiC MOSFETs.” IEEE Energy Conversion Congress and Exposition (ECCE).

4.Xing et al. (2020). “3.3-kV SiC MOSFET performance and short-circuit capability.” IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA-Asia).

5.Xing et. al. (2022). “1200-V SiC MOSFET Short-Circuit Ruggedness evaluation and Methods to Improve Withstand Time.” IEEE Journal of Emerging and Selected Topics in Power Electronics.

6.Suvendu et al. (2022). “Non-isothermal simulation of SiC DMOSFET short circuit capability.” Japanese Journal of Applied Physics.

7.Bashar et al. (2021). “Comparison of Short Circuit Failure Modes in SiC Planar MOSFETs, SiC Trench MOSFETs and SiC Cascode JFETs.” IEEE 8th Workshop on Wide Bandgap Power Devices and Applications (WiPDA).

8.Nguyen et al. (2015). “Gate oxide reliability issues of SiC MOSFETs under short-circuit operation.” IEEE Transactions on Power Electronics.

9.Kim et al. (2021). “Improved Short-Circuit Ruggedness for 1.2kV 4H-SiC MOSFET Using a Deep P-Well Implemented by Channeling Implantation.” IEEE Electron Device Letters.

10.Some details on Rohm’s fourth-generation trench SiC MOSFETs can be found at www.rohm.com/products/sic-power-devices/sic-mosfet.

11.Hatta et al. (2017). “Suppression of Short-Circuit with Embedded Source Resistance in SiC-MOSFET.” International Conference on Silicon Carbide and Related Materials.

(来源: 星辰工业电子简讯)