由于碳化硅具有不同于传统硅半导体材料的诸多特点,其能带间隙为硅的2.8倍,绝缘击穿场强为硅的5.3倍。因此在高压功率器件领域,碳化硅器件可以使用相对于硅材料更薄的外延层来达到传统硅器件相同的耐压水平,同时拥有更低的导通电阻。

目前,利用碳化硅制备沟槽功率器件的主要问题在于,在器件运行时会有很大的电场施加在栅极沟槽内的栅介质层上,这使得栅极容易被击穿,影响了器件的耐压。

因此,为了提高半导体器件的耐压性能,东微半导体在2020年11月16日申请了一项名为“半导体器件的制造方法”的技术方案(申请号:202011280137.9),申请人为苏州东微半导体股份有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项技术方案吧。

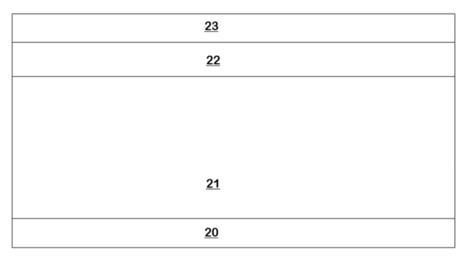

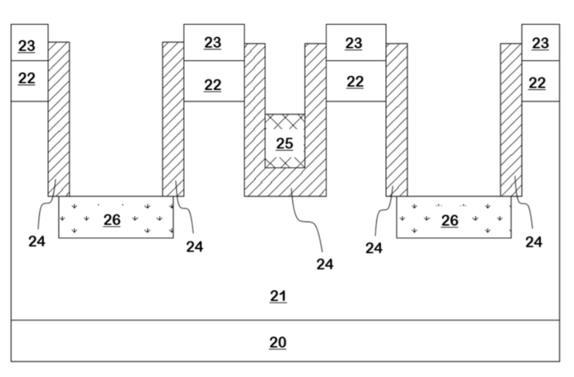

如上图,为制作该半导体器件的衬底结构,该半导体衬底包括依次层叠设置的第一n型半导体层20、第二n型半导体层21、p型半导体层22和第三n型半导体层23。其中,第一n型半导体层作为半导体器件的n型漏区,由碳化硅层所构成。

对于该衬底,会在其上进行光刻和刻蚀,从而在半导体衬底内同时形成交替间隔设置的栅极沟槽和源极沟槽。栅极沟槽的底部和源极沟槽的底部均位于第二n型半导体层内,源极沟槽的宽度大于栅极沟槽的宽度。

而对于功能区域的划分,栅极沟槽和源极沟槽之间的p型半导体层作为半导体器件的p型体区,栅极沟槽和源极沟槽之间的第三n型半导体层作为半导体器件的n型源区。

如上图,为覆盖有绝缘层以及进行各向异性刻蚀的半导体结构示意图,第一绝缘层24为覆盖栅极沟槽的内壁并覆盖源极沟槽的内壁,其通过对氧化硅进行淀积工艺形成。然后形成第一导电层并回刻,刻蚀后剩余的第一导电层在栅极沟槽内形成第一栅极25。

这是由于源极沟槽的宽度大于栅极沟槽的宽度,在形成第一导电层时,可以使第一导电层填满栅极沟槽但不填满源极沟槽。因此在刻蚀第一导电层时,通过各向异性的刻蚀方法可以直接刻蚀掉源极沟槽内的第一导电层,而在栅极沟槽内剩余一部分第一导电层以形成第一栅极。

接着,对第一绝缘层进行各向异性刻蚀,将源极沟槽下方的第二n型半导体层暴露出来。然后进行p型离子注入,在第二n型半导体层内形成位于源极沟槽下方的p型掺杂区26。或者使刻蚀后剩余的第一绝缘层的上表面与p型半导体层的上表面位置相同。

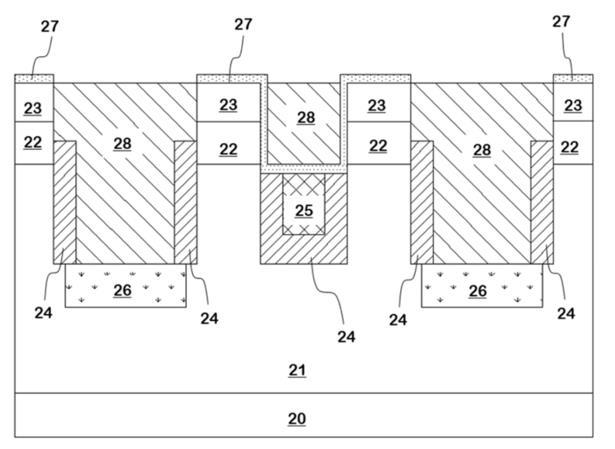

如上图,为进一步进行栅极沟槽、源极沟槽以及源极形成的半导体结构示意图。在上述形成p型掺杂区后,淀积一层光刻胶42,通过光刻工艺将栅极沟槽暴露出来。然后对栅极沟槽内的第一绝缘层进行刻蚀,使得栅极沟槽内剩余的第一绝缘层的上表面不高于p型半导体层的下表面。

接着,去除掉光刻胶后形成第二绝缘层27,然后淀积一层光刻胶43。通过光刻工艺将源极沟槽暴露出来,然后对源极沟槽内的第二绝缘层进行刻蚀,从而去除掉源极沟槽内的第二绝缘层。之后,继续对源极沟槽内的第一绝缘层进行各向异性刻蚀,使得p型半导体层在源极沟槽的侧壁位置处暴露出来。

最后,在上述结构上形成第二导电层28,并对第二导电层进行刻蚀,刻蚀后剩余的第二导电层在栅极沟槽内形成第二栅极并在源极沟槽内形成源极。

以上就是东微半导体发明的基于碳化硅的半导体器件制造方案,该方案中的栅极沟槽和源极沟槽在同一步刻蚀工艺中同时形成,并且源极沟槽下方的p型掺杂区可以增加源极沟槽底部附近的电场,把半导体器件内的最高电场限定在源极沟槽的底部附近,从而保护栅极沟槽内的栅极不容易被击穿,并有效提高了半导体器件的耐压。