一、第三代半导体:闻起来有点香

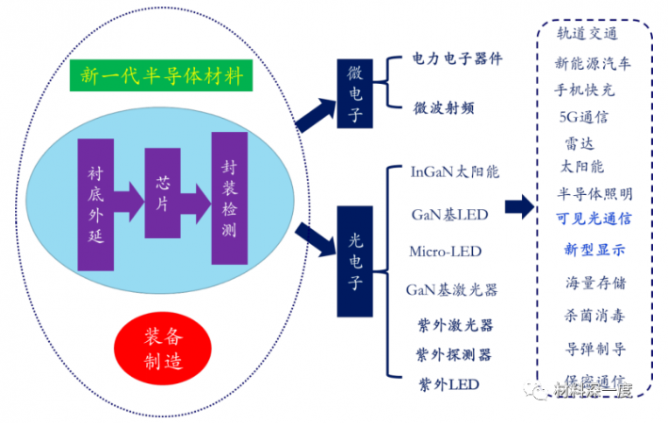

第三代半导体包括碳化硅(SiC)、氮化镓(GaN)、氮化铝(AlN)、金刚石、氧化镓等,具有禁带宽、击穿电场强度高、饱和电子迁移速率高、热导率大、介电常数小、抗辐射能力强等优点。以第三代半导体材料为基础制备的电子器件在半导体照明、新一代移动通信、新一代快充电源、雷达、新能源汽车、轨道交通和航空航天等领域都有重要应用,对国家的产业升级、节能减排和国防安全具有重要战略意义,是新基建、消费电子和军事国防的核心元器件,也是当前全球信息制造产业竞争焦点。以GaN基LED为基础的半导体照明形成了千亿美元规模的产业,年节电近两千亿度;以SiC基MOSFET和AlGaN/GaN HEMT结构为代表的功率器件正在显著影响和改变人们的生活方式,SiC是目前能实现万伏千安的唯一材料,可实现电力电子装置的紧凑化和小型化(体积减小40%,能量损耗减少50%),是电动汽车逆变器的不可缺少核心器件;GaN是同时实现高频、大宽带和大功率的唯一材料,基于AlGaN/GaN HEMT结构的微波功率器件是5G基站和相控阵雷达发射单元的核心;GaN是唯一覆盖从红外到紫外的半导体材料,基于GaN材料的光电器件在可见光通信、新型显示、杀菌消毒、海量存储、导弹制导等方面有重要应用。

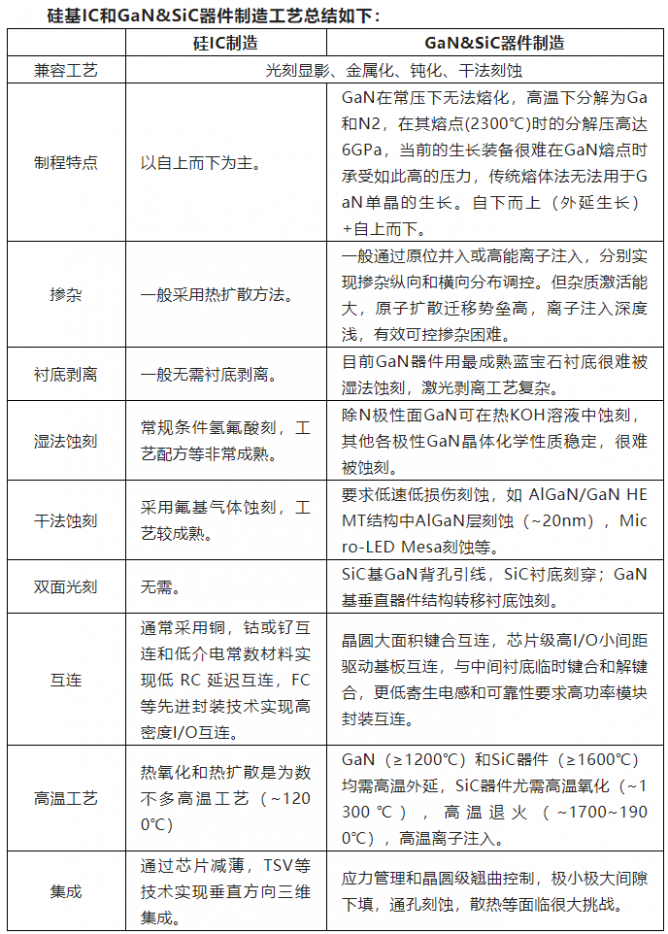

那么问题来了:为什么在台积电、英特尔带领硅基IC先进制造向3nm, 2nm的极限尺度进军时,第三代半导体的器件特征尺寸却徘徊在数百纳米, 甚至微米?比如被认为是未来显示重要技术的Micro-LED,目前像素尺寸能做到2微米,像素密度到10000,已经是非常先进水平。

二、第三代半导体:啃起来有点硬

第三代半导体材料具有和传统半导体硅不同的材料性质,具有“五高”特征:高电压,高工作温度,高频,高功率密度和高效率,导致其器件制造工艺和技术上差别很大。从某种程度上看,第三代半导体器件制造具有“极端制造”特点。

1.薄膜沉积:

GaN在常压下无法熔化,高温下分解为Ga和N2,在其熔点(2300℃)时的分解压高达6GPa。当前生长装备很难在维持GaN熔点温度下,同时承受如此高的压力。因此传统熔体法无法用于GaN单晶的生长。GaN器件以异质外延、水平结构路线为主。MOCVD外延是构造GaN器件的核心,而衬底选择是关键,决定器件技术路线。目前衬底主要有异质蓝宝石、SiC和Si。有限的衬底选择和外延严苛条件使器件设计和制造受到一定限制。从根本上突破衬底的限制将更充分释放GaN等第三代半导体器件潜能。美国Los Alamos National Laboratory孵化的iBeam Materials公司,利用离子束辅助沉积技术,可在包括超薄金属片等多晶甚至非晶衬底上通过常规磁控溅射等物理沉积方法,获得晶向织构可控的成核层,然后继续外延生长获得质量良好的GaN材料,用于制作LED和晶体管器件,进一步用于Micro-LED显示,柔性电子器件等(Phys. Status Solidi A2020, 1900800,ICNS-13 2019 July 8, 2019 l Bellevue, Washington, USA)。然而晶向织构可控成核沉积技术还面临多相多晶态竞争可控调制,粗糙或大尺寸衬底原子迁移动力学控制,衬底晶格-原子吸附迁移热力学-动力学综合调控,以及辅助沉积装备定制设计 等制造科学、工艺和设备问题。

2.掺杂:

半导体掺杂一般可通过材料生长原位并入,器件制造中热扩散和离子注入等方法实现。传统硅掺杂一般通过热扩散实现,利用高温驱动杂质进入硅的晶体结构。第三代特征使掺杂杂质激活率低,同时其强化学键特征使杂质原子扩散距离短,注入深度浅。因此第三代半导体一般通过外延生长过程原位掺杂,和器件阶段离子注入工艺,分别实现对掺杂原子的纵向和横向分布控制,通过热扩散实现浓度和分布可控掺杂非常困难。离子注入掺杂则面临晶格严重损伤,高温晶圆翘曲带来的掺杂均匀性和同后续工艺制成兼容性,以及离子注入深度有限导致很多器件需要多次重复材料生长-离子注入步骤等问题。原位生长并入掺杂不能实现掺杂横向梯度可控。比如, MOCVD外延较难实现横向梯度可控掺杂。第三代半导体禁带宽度较大,杂质激活能随禁带宽度增大而增大。原位p型掺杂目前能达到的最高空穴浓度仅为10e18级别,比对应电子浓度小两到三个数量级。

3.衬底剥离:

衬底剥离主要是GaN基器件。一般在异质衬底上外延获得GaN基材料。蓝宝石是目前市场上最重要的衬底, 在LED芯片用衬底市场占据绝对主导地位,具有晶格匹配性较好,工艺成熟、产品质量优,透光性极高,价格适中,出光效率高等优点。同时存在热导率较低,电导性差,折射率高导致出光率相对较低等缺点。导热性差虽然在器件小电流工作中没有暴露明显不足,却在功率型器件大电流工作下问题十分突出。将蓝宝石衬底剥离去除,并将器件转移至导电导热良好的衬底上,是制备GaN基大功率LED\高PPI Micro-LED\功率器件的重要选择。衬底剥离是最关键工艺。蓝宝石化学性质非常稳定,一般的酸碱溶液等难以蚀刻去除。香港应科院等提出机械磨抛法,但是要求很高。目前一般是采用KrF深紫外激光照射GaN/蓝宝石界面,使GaN分解,从而剥离衬底。但是分解过程中急速产生的N2需要释放,需要工艺上设计释放通道等。目前Micro-LED显示被广泛看好,同传统LED和Mini-LED不同,Micro-LED的衬底需要去除。这对蓝宝石衬底路线带来较大挑战。

4.蚀刻:

GaN材料和蓝宝石衬底的化学惰性使湿法蚀刻和衬底剥离较困难。这提高了器件制程的窗口和可靠性,但同时也将极大限制器件结构和功能实现,也对某些器件特殊制程和工艺带来很大挑战。如GaN晶体在除了氮极性面的包括Ga极性、半极性和非极性面均难被常规酸碱蚀刻,这增加了传统侧向型GaN基LED的表面粗化工艺,以及晶圆减薄难度。传统硅CMP可以在化学和机械磨抛共同作用下达到原子级别精度,但对于第三代半导体,在纯粹机械磨抛作用下很难实现厚度和表面平整度的高精控制。第三代半导体高硬度等特性对晶圆抛光,研磨,切割工艺有特殊要求。基于异质外延的应力型器件对低损伤芯片加工工艺也提出更高要求,如 AlGaN/GaN HEMT结构中AlGaN层刻蚀(~20nm),Micro-LEDs Mesa刻蚀等。SiC基GaN射频器件背孔引线需要SiC衬底刻穿,GaN基垂直器件结构转移衬底蚀刻等则需要双面光刻工艺。

5.互连:

互连工艺包括芯片级互连和封装级互连。前者包括GaN器件原衬底剥离后同新衬底互连,器件同驱动电路基板互连等,后者包括功率芯片与DBC衬板互连,芯片与电路引线键和互连等。以GaN基Micro-LED为例,尺寸向亚10μm推进,芯片的I/O数目和密度都增加,需要更高精度、更高工艺兼容性、更高可靠性的芯片-驱动衬底互连技术。传统键合工艺需要高温高压条件,对准精度低,难以满足高可靠高密度器件阵列互连需求。对于SiC基功率模块,传统硅基功率模块引线键合用铝线,可靠性低,在高温高功率服役条件下面临电热力各方面问题和挑战。采用多芯片并联的SiC MOSFET功率模块,Vth较低,短路耐量较小,需要低的寄生电容和电感,因为高的开关速度将产生高dv/dt 与 di/dt,更高的关断过电压、更大的开关振荡,增加器件的开关损耗和 EMI 噪声。

6.高温工艺:

离子注入和注入后的退火都需要高温工艺,而SiC基MOSFET器件则还需要高温氧化工艺。这也是第三代半导体器件制造工艺和硅基工艺的一个显著区别。

7.散热:

而高结温高功率密度SiC MOSFET等功率器件和GaN基HEMT高频器件对芯片和模块级的互连散热等工艺提出了很高的要求。高功率密度器件(如SiC MOSFET(体积不到IGBT的1/5), 用于5G宏基站的100W-300W级的极大功率GaN射频器件),或高密度热源器件(如GaN基Micro-LED)等器件的高效散热需求。三维堆叠封装氮化镓芯片功率密度大、体积小、界面多、散热面积小,传统的二维芯片的散热方式往往很难用于3D封装器件,使得热管理成为3D 堆叠封装所面临的最严峻的挑战:GaN器件本身的自热问题,高电压、大电流的工作条件下,其本身在沟道处会产生一定的热量,该热量会导致器件沟道内温度迅速上升;垂直方向上的芯片堆叠增加了功率密度,层间低热导率介质层的存在导致了散热问题恶化,进一步增加堆叠芯片从顶部到热沉之间的热阻;垂直方向上的热串扰,特别在高功率芯片与低功率温度敏感元件之间的热流动。

8.集成:

异质集成或者三维集成第三代半导体涉及到多材料(第三代半导体、金属、有机物等),多域(芯片、模块、系统),多物理场(电场、电磁波、热、力)和多尺度(纳米到微米到毫米),加之第三代半导体器件本身的高压、高功率、高温、高频、高密度I/O等属性,需要进行工艺协同兼容。如综合防短路和防击穿技术,包括综合版图设计技术,应力管理和晶圆级翘曲控制技术,极小极大间隙下填技术,防止高密度互连下短路和高电压击穿。IC硅器件间垂直互连一般通过TSV,第三代半导体同硅在材料力学参数区别,通孔蚀刻,或者激光打孔工艺面临较大不确定性。

三、第三代半导体器件制造:从1到N的挑战

一项技术从发明走向应用,从1到N,在很多时候,比从0到1要更为重要,更为艰辛和漫长。硅基集成电路之所以能从从1到N, 以摩尔定律速度推进,并行高效的平面工艺发挥关键作用。发明基于平面工艺集成电路的诺伊斯,和发明晶体管的肖克利同样伟大。

二维metasurface及平面光学元件,比三维metamaterials更吸引产研人员的兴趣,也在于相比于后者,得益于平面工艺的成熟,前者从1到N的可能性要大得多。三维metamaterials的制造是个大问题。德国Karlsruhe Institute of Technology (KIT)研发的Nanoscrible等基于双光子吸收的三维加工制造设备,问题还是很多。

先进封装被视为延续摩尔定律的重要技术选择,2.5D/3D的先进封装能否更多地渗入,高效低成本的制造工艺也是关键。平面工艺并不等同平面结构,3D结构也当然可以基于平面工艺。

第三代半导体器件中,LED已经实现了从1到N,而Micro-LED显示则是面临巨量转移等从1到N关键技术的挑战。以4K电视为例,4K通常指4096*2160分辨率,假设每像素点为三个R/G/B晶粒,制作一台4K电视便需转移高达2600万颗晶粒—即使每次转移1万颗,也需重复2400次。巨量转移不是硅基IC的成熟工艺:比如M1 芯片拥有 160 亿个晶体管, M1 Ultra上的晶体数量多达1140亿,巨量转移是不可能的。

第三代半导体的科学研究,也许可以更多从0到1探索发现;第三代半导体制造,也许需要更多考虑从1到N的创新突破,更多借鉴利用硅的成熟制造工艺。

四、第三代半导体制造: 硬骨头,还要硬啃

IC制造和第三代半导体制造,除了技术上,还有很多其他方面的差别。IC产业相对非常成熟,产值很大,产业分工从最初的IDM到现在的Fabless+ Foundry模式占据上风,IC制造在IC产业中起着举足轻重的作用。因其产值大,产业链成熟,IC制造的即使较小的工艺进步或创新,都可能形成很大的放大作用,对企业本身和产业格局趋势产生重要影响。比如130nm Cu互连工艺,沉浸式光刻机。第三代半导体技术目前相对没那么成熟,整体和各个细分产品的产值也还较小,还处在群雄逐鹿时代,企业倾向IDM模式,以便更好控制成本、质量和供应链等。高校、研究所企业等第三代半导体方面研究,更多是针对产品,如Micro-LED、UVC LED、射频微波器件、功率半导体器件等,而专门针对第三代半导体中的共性工艺或制程研究相对较少。相对来说,越往材料和底层的工艺会得到更多些关注和研究,因为其可能的使能范围,放大系数会相对大。如诺奖得主S. Nakamura等解决p型GaN掺杂难题,除了部分n型单极型器件,可以用于所有的双极型和复合光电子和电子GaN器件。中科院长光所、西安电子科技大学、美国耶鲁大学等在更宽禁带AlGaN掺杂、GaN可控湿法蚀刻、第三代半导体激光切割等研究屡有进展。第三代半导体设备厂商当然会结合工艺研发,但和IC制造工艺研发还是有所区别。

最近,美国对华实施出口新禁令,其中包括宽禁带半导体氧化镓和金刚石。第三代半导体这块硬骨头,还要硬啃下去。

作者简介:

汪炼成,中南大学特聘教授,高性能复杂制造国家重点实验室研究员,从事第三代半导体器件研究。

作者简介:

汪炼成,中南大学特聘教授,高性能复杂制造国家重点实验室研究员,从事第三代半导体器件研究。