PGL22G开发板中包含一个以太网接口,紫光同创FPGA通过RGMII接口与外部PHY芯片互连。而在千兆模式下,RGMII的运行速度为125MHz的双沿并行数据采样(DDR)。

在本工程中计划测试以太网在千兆速率下,以满流量收发包时的丢包率问题。个人认为如果千兆以太网测试能够达到要求的话,该芯片应该可以满足大多数中低端的应用场景。

整个设计的系统结构如下图所示:其中①串口模块用作命令行交互控制工具,用于对内部模块进行控制和内部模块状态信息输出,从而方便调试;②以太网0包含一个完整的MAC以及报文产生、报文解析模块、报文统计功能,是本工程的主要测试对象;③以太网1包含一个完整的MAC,在本工程中没有实际用途,仅用于“消耗”FPGA资源,从而便于测试FPGA在资源“压力”下的性能。

由于千兆以太网在工作时需要125MHz的时钟,因此本设计全局系统时钟初步定为125MHz。由于本工程已有一些现成的模块加上ALINX提供的参考工程,设计/整理/仿真一步步走下来,很快就可以上PANGO软件来实现了。

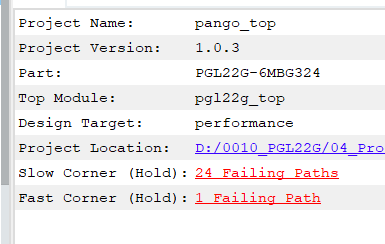

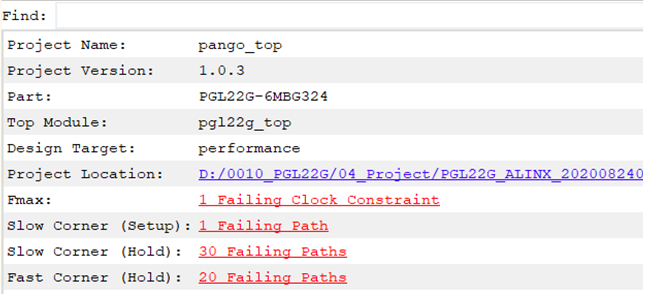

第一次运行结果如下,出现了一众时序违规路径,125MHz的主工作时钟频率无法满足。

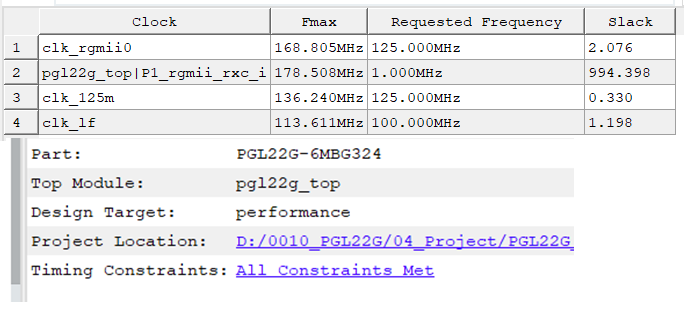

首先想到的是对系统工作时钟进行修改,将系统时钟频率降低为100MHz,仅RGMII接口模块部分功能使用125MHz工作频率。

第二次运行结果,时序通过(实际运行了多次,生成时钟约束、跨时钟域路径false等约束被逐渐加入)。结果还算不错。

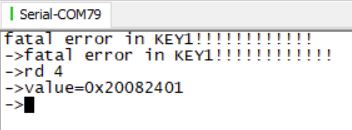

上板运行,通过串口输入到FPGA或FPGA内部信息打印输出均正常。

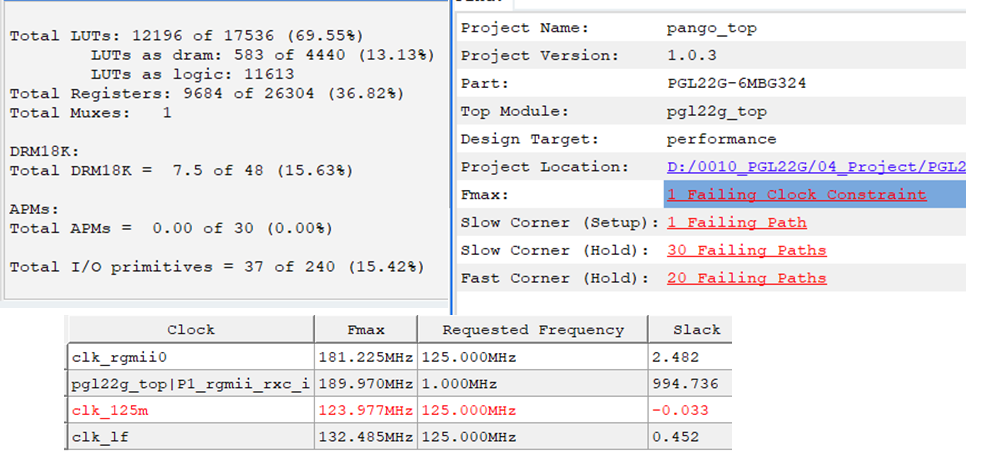

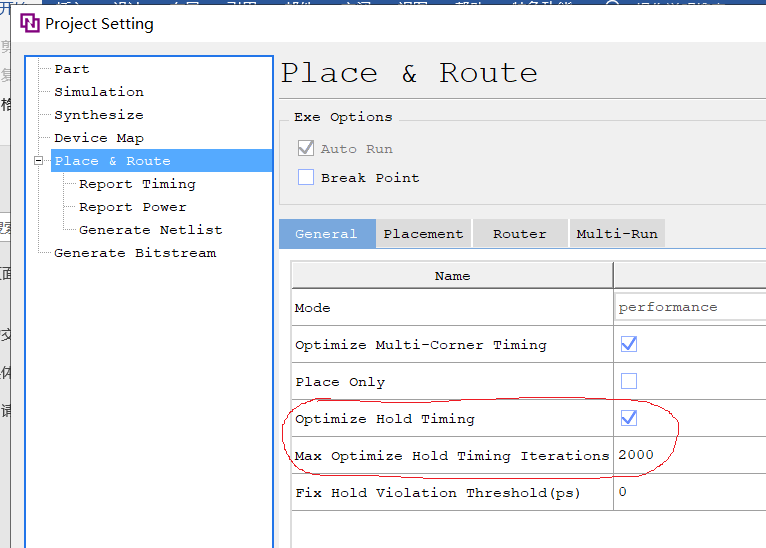

再次尝试125MHz的系统时钟。分析第一步中的时序falling结果,发现是hold时序路径违规数比较多。其实在多次尝试后发现出现hold时序违规的次数比较多,经验表明可以通过工程设置来尝试一下,在软件中逐个设置选项查看,果然有一项可以设置:

勾选Optimize Hold Timing选项并将最大优化值改大一些,再次运行。但是结果似乎不太明显。

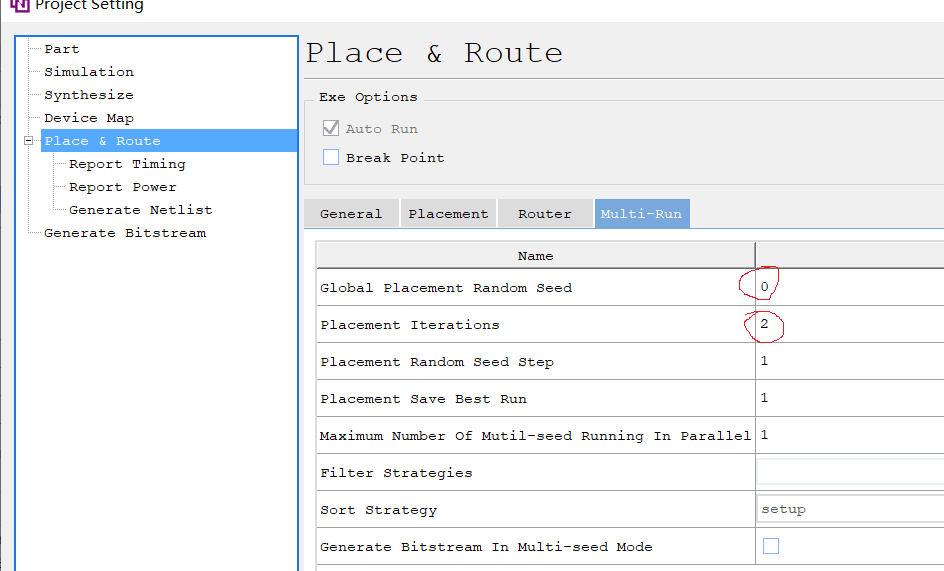

为验证FPGA性能,暂时不考虑使用设计优化的方式去优化时序,继续查找通过设置工具的实现条件来尝试。这里主要尝试改变如下图中的2个条件。通过多次编译发现,改变“Seed”的效果不太明显,但是将迭代次数“Placement Iteration”增加可以起到比较明显的效果(同时编译时间会变长)。

时序有好转但是还没有达到想要的时钟频率。