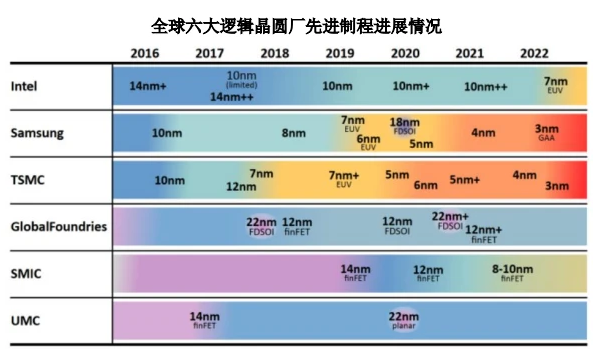

随着 5G、人工智能、智慧交通等消费电子、汽车电子、计算机等应用领域先进技术的发展,下游应用场景对于芯片性能提出更高的要求,推动芯片制程升 级。国内外晶圆厂加紧对于半导体新制程的研发,全球晶圆制造龙头企业台积电、 三星等均已向 5nm 以下制程突破;大陆晶圆制造龙头中芯国际也在加紧 12nm 以 下制程工艺的研发。

资料来源:IC Insights(Intel 指英特尔;Samsung 指三星;TSMC 指台积电;Global Foundries 指格罗方德;SMIC 指中芯国际;UMC 指台联电)

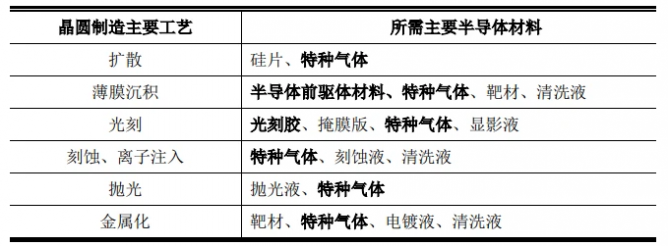

而芯片制造技术升级需要半导体设备和材料作为支撑。常见晶圆制造工艺所 需半导体材料如下所示:

资料来源:ittbank

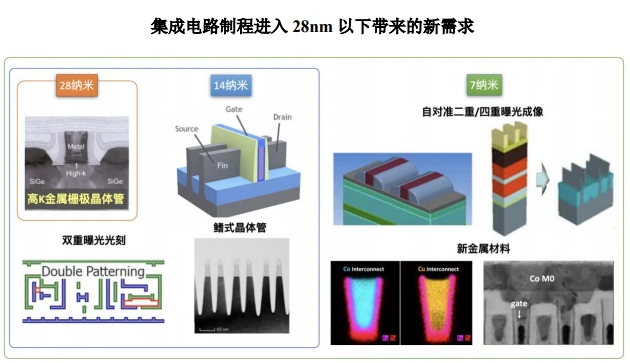

近年来集成电路制造技术快速发展,新制程带来新的工艺与材料的变化。集 成电路制造进入 28nm/14nm/7nm 制程后,新的晶体管器件、新的工艺和材料不 断引入,新的晶体管器件如高 K 金属栅极(HKMG)晶体管、鳍式场效应晶体 管(FinFET),新的工艺如自对准多重成像工艺等,新的材料如钴金属导电层; 同时,先进半导体制程呈现向三维结构转化的趋势。以上集成电路领域的新变化 对晶圆制造主要工艺薄膜沉积工艺——特别是作为这一工艺核心的先进前驱体 材料——提出了更高的要求。

如上图所示,高 K 金属栅极(HKMG)晶体管是集成电路制程进入 28nm 的 新材料,由于传统二氧化硅栅极晶体管在 28nm 制程后漏电情况大幅增加影响芯片性能,而高 K 金属栅极(HKMG)晶体管则有效解决了这一问题。

双重曝光光刻和鳍式场效应晶体管(FinFET)是集成电路制程进入 14nm 的 新工艺和新器件,其中在双重曝光光刻工艺结合 ArF 浸没式光刻胶可以达到 14nm 以下的集成电路制程;3D 结构的 FinFET 工艺相对于传统的平面晶体管而言减小了晶体管的短沟道效应,同时能够更好地对沟道进行静电控制,FiFET 工 艺也需要薄膜沉积工艺及半导体前驱体材料能够填充更小、更高纵深比的沟槽。 进入集成电路 7nm 后,自对准二重/四重曝光成像技术和钴元素等新金属材 料制成的薄膜得到应用。

自对准二重/四重曝光成像技术系通过多重曝光实现小 尺寸工艺,需要在低温环境下活性好且镀膜均匀的前驱体材料;钴元素则是在新 的技术需求下替代钨元素的新材料,具体表现在含钴的金属前驱体材料等。

此外,更高端的制程工艺需要更加先进薄膜沉积技术(如原子层薄膜沉积 ALD 技术),该技术的先进性以先进 ALD 前驱体材料作为核心支撑;7nm 以下 集成电路制程也需要 EUV 光刻胶作为必备的生产材料。

(来源:思瀚产业研究院 南大光电)