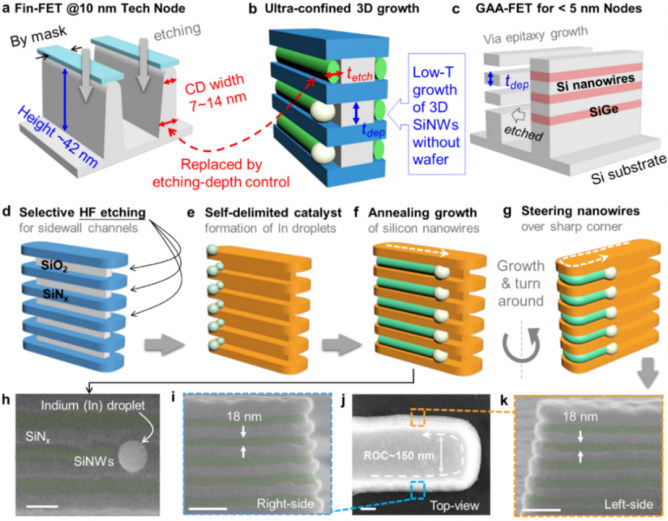

后摩尔时代集成电路的发展,尤其是10 nm工艺节点之后,越来越依赖深紫外(DUV)和极深紫外(EUV)光刻技术定义沟道特征尺寸(CD)。特别是作为围栅结构晶体管(GAA FET)的关键—CD <10 nm的三维堆叠纳米线晶硅沟道目前只能通过最先进的“自上而下”光刻刻蚀工艺实现。随着沟道特征尺寸的下降,其工艺复杂度和成本快速上升。更为重要的是,由于技术和核心设备的封锁,使得我国发展这项技术面临一系列极端难题。相较而言,“自下而上”的催化生长技术则提供了一种更为灵活、高效和低成本的硅纳米线制备路径。然而,面向大规模可靠集成应用,尤其是产业化电子器件,其主要技术挑战在于:如何在三维空间实现CD小于10 nm的纳米线精确控制生长、定位以及规则排布。

成果掠影

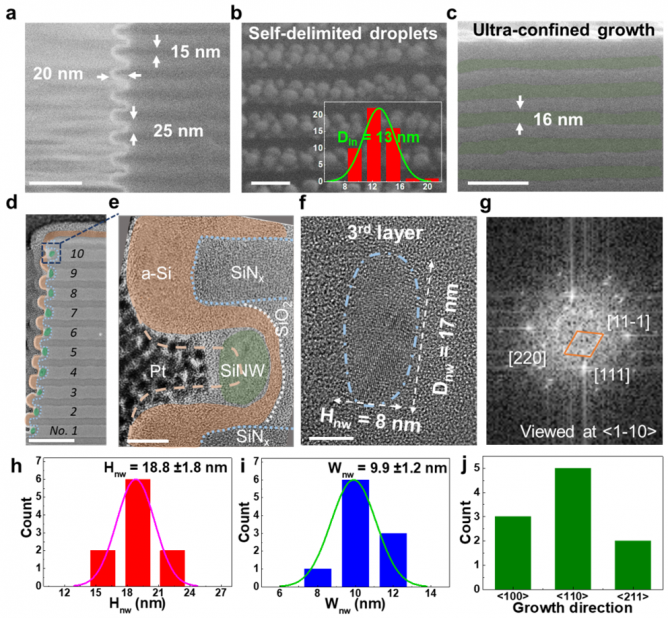

针对这一难题,南京大学电子学院余林蔚教授团队基于团队自主创新的平面IPSLS纳米线生长模式,采用侧壁精细沟槽引导技术实现了三维堆叠超细、均匀纳米线的“超限制调控生长”,首次将其宽度和高度分为微缩至Wnw= 9.9 ± 1.2 nm 和Hnw= 18.8 ± 1.8 nm,达到10 nm技术节点特征尺寸,并能实现可靠批量制备。此外,硅纳米线沟道的截面形貌可以通过沟槽结构方便地从高而窄的“鳍状”结构调控为扁而宽的“纳米片”状结构--预示着一个关键的纳米线沟道形貌调控新维度。同时,此次工作中还提出通过一次连续弯道生长,连续获得多排紧密排列的堆叠纳米线沟道,最小化了催化金属的使用量。另外,该文还展示了原型场效应晶体管器件。

核心创新点

以“自下而上”的催化生长技术,在无需使用超高精度EUV光刻技术的前提下,生长集成特征尺寸小于10 nm的超细三维堆叠硅纳米线阵列。

数据概览

与传统“自上而下”工艺需超高精度EUV光刻机定义沟槽的特征尺寸不同,侧壁生长纳米线被稳定的限制在沟槽中,其高度由氧化硅层的沉积后续控制,而宽度则由沟槽深度决定。无需高精度光刻就可将纳米线的特征尺寸微缩到10 nm以下。

图1 “超限制”侧壁沟槽引导超细堆叠纳米线生长流程以及与传统特征尺寸控制方式比较

为了实现纳米线特征尺寸的微缩,本文提出一种新的自限制催化颗粒形成策略,避免颗粒跨沟槽融合并抑制其大小涨落。截面TEM表明每个沟槽中都有且仅有一根纳米线生长,且其特征尺寸小于10 纳米,截面为“鳍状”结构。

图2 三维堆叠纳米线结构表征和特征尺寸统计。

成果启示

这项成果突破,有望为我国自主创新和发展建立的可控GAA- FET技术路径奠定新的关键技术基础,从而进一步释放“自下而上”生长集成技术在探索先进三维逻辑、传感和NEMS结构器件的应用潜能。值得一提的是,此三维生长集成策略无需晶硅衬底作为基础,可在低温下(<350℃)可靠制备高品质单晶纳米沟道,故而非常适用于探索实现真正的三维一体化集成技术(3D Monolithic Integration),为突破冯诺依曼框架的存算一体化新构架及类脑计算应用提供了一种可靠的全新技术方案和路线。

该工作近期以 “Ultra-confined catalytic growth integration of sub-10 nm 3D stacked silicon nanowires via self-delimited droplet formation strategy” 发表于Small上, DOI: 10.1002/smll.202204390。其中,博士胡瑞金(2022年6月毕业,现任职扬州大学)为第一作者,余林蔚教授为通讯作者,研究工作得到了南京大学徐骏教授、施毅教授、王军转教授、刘宗光副研究员的大力支持,以及国家自然科学基金委重大研究计划重点项目及华为-南京大学专项合作等基金项目资助,在此一并表示衷心感谢!

文章链接:

https://onlinelibrary.wiley.com/doi/10.1002/smll.202204390

前期相关工作:

Hu, R.; Xu, S.; Wang, J.; Shi, Y.; Xu, J.; Chen, K.; Yu, L.* Unprecedented Uniform 3D Growth Integration of 10-Layer Stacked Si Nanowires on Tightly Confined Sidewall Grooves. Nano Lett. 2020, 20(10), 7489-7497.

Hu, R.; Ma H.; Yin H.; Xu, J.; Chen, K.; Yu, L.* Facile 3D integration of Si nanowires on Bosch-etched sidewalls for stacked channel transistors. Nanoscale 2020, 12, 2787-2792.

Wu X.; Ma H.; Yin H.; Pan D.; Wang J.; Yu, L. *; Xu, J.; Chen, K. 3D Sidewall Integration of Ultrahigh-Density Silicon Nanowires for Stacked Channel. Adv. Electron. Mater. 2019, 5, 1800627.

Sun, Y.; Dong, T.; Yu, L.*; Xu, J.*; Chen, K. Planar Growth, Integration, and Applications of Semiconducting Nanowires. Adv. Mater. 2020, 32(27), 1903945.

Yin, H.; Yang, H.; Xu, S.; Pan, D. *; Xu, J.; Chen, K.; Yu, L. *High Performance Si Nanowire TFTs With Ultrahigh on/off Current Ratio and Steep Subthreshold Swing. IEEE Electr. Device L. 2020,41(1), 46-49.

(来源:材料人)