几十年来,硅基功率晶体管(MOSFET、场效应晶体管)构成了功率转换系统的支柱,可将交流电 (AC) 转换为直流电 (DC),反之亦然,或将直流电从低压转换为高压。在寻求可以提高开关速度的替代品时,氮化镓 (GaN) 迅速成为领先的候选材料之一。GaN/AlGaN 材料体系表现出更高的电子迁移率和更高的击穿临界电场。结合高电子迁移率晶体管 (HEMT) 架构,与同类硅解决方案相比,它使器件和 IC 具有更高的击穿强度、更快的开关速度、更低的电导损耗和更小的占位面积。

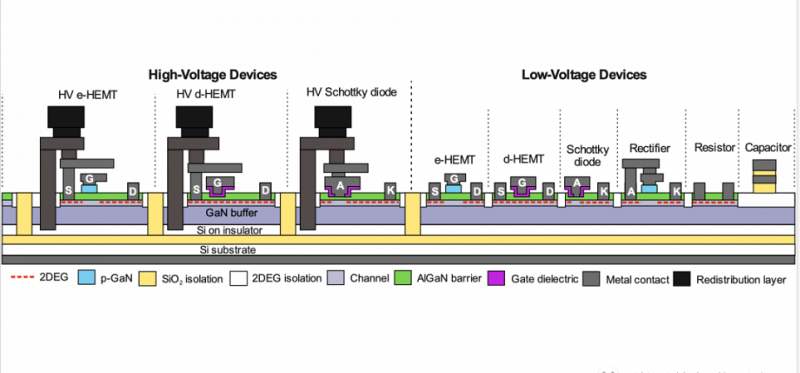

IMEC 200V GaN-on-SOI 功率 IC 技术和组件的横截面示意图。该工艺具有 E/D 模式 HEMT、肖特基二极管、电阻器、电容器的单片共集成,并包括先进的工艺模块(深沟槽隔离、衬底接触、再分布层......)

今天,大多数 GaN 电源系统由多个芯片组成。基于 GaN 的器件在组装到印刷电路板上之前作为分立元件组装。这种方法的缺点是存在影响器件性能的寄生电感。“以驱动器为例,在单独的芯片上带有驱动器的分立晶体管受到驱动器输出级和晶体管输入之间以及半桥开关节点之间的寄生电感的影响。GaN HEMT 具有非常高的开关速度,当寄生电感未被抑制时,这会导致振铃(ringing),即信号的不希望的振荡。减少寄生效应和利用 GaN 卓越开关速度的最佳方法是将驱动器和 HEMT 集成在同一芯片上,”来自IMEC的Stefaan Decoutere 解释道。

“同时,它减少了半桥中两个晶体管之间的死区时间控制,其中一个晶体管必须在另一个晶体管打开时关闭。在这期间,电源和地之间存在短路,或死区时间。在芯片上集成所有组件将解决振铃问题,减少死区时间,并最终提高转换器的电源效率。”

d 模式 HEMT 的共集成

Imec 已经在绝缘体上硅 (SOI) 基板上单片集成构建块(例如驱动器、半桥和控制/保护电路)取得了巨大进展。现在,研究人员已经成功地在产品组合中添加了两个广受欢迎的组件:d 模式(耗尽模式)HEMT 和肖特基二极管。

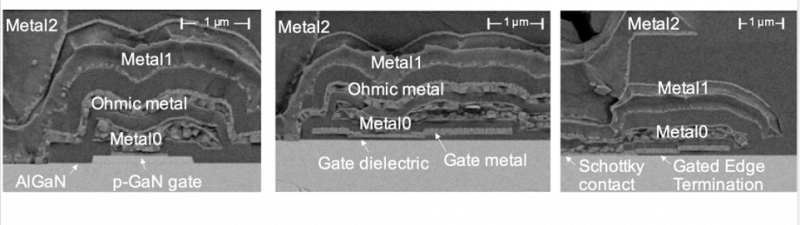

在 200 mm GaN-on-SOI 衬底上制造的高压组件的工艺横截面 (a) e 模式 pGaN-HEMT (b) d 模式 MIS-HEMT,(c) 肖特基势垒二极管。所有器件都包括基于前端和互连金属层并由介电层隔开的金属场板

提高 GaN 功率 IC 的全部性能的主要障碍之一仍然是寻找合适的解决方案来解决 GaN 中缺乏具有可接受性能的 p 沟道器件的问题。CMOS 技术使用互补且更对称的 p 型和 n 型 FET 对,基于两种 FET 的空穴和电子迁移率。然而,在 GaN 中,空穴的迁移率比电子的迁移率差 60 倍左右;在硅中,这只是 2 倍。这意味着以空穴为主要载流子的 p 沟道器件将比 n 沟道对应器件大 60 倍,而且效率极低。一种广泛使用的替代方法是用电阻器代替 P-MOS。电阻晶体管逻辑 (RTL) 已用于 GaN IC,但在开关时间和功耗之间表现出权衡。

“我们通过在 SOI 上的功能性 e-mode HEMT 平台上共同集成 d-mode HEMTS,提高了 GaN IC 的性能。增强和耗尽模式是指在零源电压下的 ON(d 模式)或 OFF(e 模式)状态,导致晶体管中的电流流动(或不流动)。我们期望从 RTL 向直接耦合 FET 逻辑迈出一步将提高速度并降低电路的功耗,”Stefaan Decoutere 说。

具有低泄漏电流的肖特基二极管

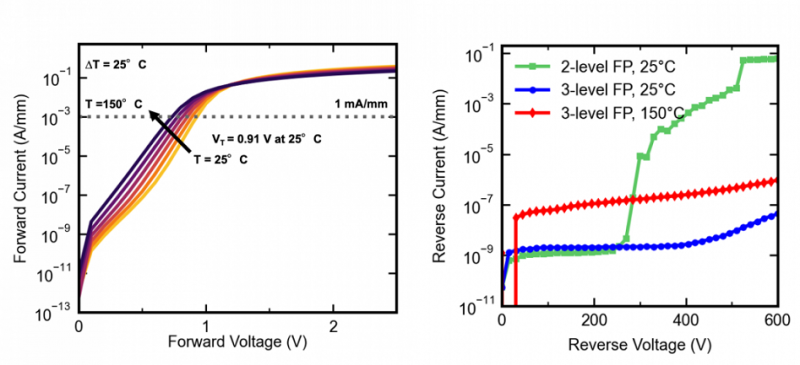

肖特基势垒二极管的集成进一步提高了 GaN 功率 IC 的功率效率。与硅二极管相比,它们可以在相同的导通电阻下承受更高的电压,或者在相同的击穿电压下承受更低的导通电阻。“制造肖特基势垒二极管的挑战是获得低导通电压和低泄漏水平。不幸的是,当您瞄准较低的导通电压时,您最终会遇到一个小的屏障来阻止泄漏电流。肖特基二极管因漏电流高而臭名昭著。与传统 GaN 肖特基势垒二极管相比,Imec 专有的栅极边缘端接肖特基势垒二极管架构 (GET-SBD) 可实现约 0.8 伏的低开启电压,同时将漏电流降低几个数量级,

制造的 GET-SBD 的特性显示(左)在 25°C 下以半对数刻度显示 0.91V 的低开启电压,以及(右)两种不同阳极的低反向漏电流(25°C 时为 2 nA/mm)在 25 和 150°C 下评估的场板配置。

快速开关和高电压

GaN 是高功率应用的首选材料,因为导致晶体管击穿的临界电压(击穿电压)比硅高 10 倍。但对于低功率应用,GaN 仍然具有优于硅的优势,因为它具有出色的开关速度。“我们创建的基于 GaN 的 IC 为更小、更高效的 DC/DC 转换器和负载点 (PoL) 转换器开辟了道路。例如,智能手机、平板电脑或笔记本电脑包含可在不同电压下工作的芯片,因此它们需要 AC/DC 转换器来为电池充电,并需要设备内部的 PoL 转换器来产生不同的电压。这些组件不仅包括开关,还包括变压器、电容器和电感器。晶体管开关速度越快,这些组件就越小,

Stefaan Decoutere:“快速充电器构成了当今 GaN 的最大市场,其次是用于服务器、汽车行业和可再生能源的电源。预计使用 GaN 的电源在系统级更可靠。它们的外形尺寸和重量更小,从而减少了材料清单,从而降低了成本。

正在研究的垂直设备

“我们将专注于提高现有平台的性能,并进行进一步的可靠性测试。我们目前提供用于原型设计的 200V 和 650V 平台,很快就会推出 100V。对于具有集成组件的 GaN-IC,1200V 大功率平台可能不会产生显着的改进。电压越高,组件变得越慢。因此,可能没有必要在芯片上集成驱动程序;模拟会告诉我们。”

“与此同时,我们正在寻找分立 1200V 器件的替代品,使 GaN 技术能够用于电动汽车等最高电压功率应用。具有横向拓扑的晶体管是当今占主导地位的 GaN 器件架构。这些器件的三个端子(源极、栅极和漏极)位于同一平面的表面,因此电场是横向的,跨越 GaN 缓冲层和部分后端(金属化、氧化物)。在垂直器件中,源极和栅极位于表面,而漏极位于外延叠层的底部。在这种情况下,电场流过整个堆栈。决定器件击穿电压的是源漏分离,较大的分离可以保护通道不被击穿。然而,横向放置的源极和漏极之间的距离越大,器件越大。因为 1200V 设备的芯片会变得太大,横向架构通常建议最高 650V。相反,对于垂直器件,使用更高的电压归结为创建更厚的外延堆叠,因为源极和漏极位于堆叠的不同端。芯片的表面积没有增加,”Stefaan Decoutere 总结道。