0 引言

功率器件是电力电子技术的核心,在电力电子技术朝着高频、高功率密度发展的方向上扮演着至关重要的角色。目前,硅(silicon,Si)器件的发展已经十分成熟,在 600V 以下的应用,Si 基金氧半场效晶体管 (metal-oxide-semiconductor field effecttransistor,MOSFET)占据主流,而 Si 基超级结器件和绝缘栅双极型晶体管 (insulator gate bipolartransistor,IGBT)则主导了 0.6~6.5kV 的高压应用市场。尽管如此,受限于硅材料特性的限制,硅器件的发展空间已经较为有限。例如,目前 Si 基 IGBT耐压极限为 6.5kV,工作温度低于 175℃,且由于双极性导通模式,器件开关速度较低,限制了其在高频应用中的推广。

近 20 多年来,以碳化硅(silicon carbide,SiC)为代表的宽禁带半导体器件,受到了广泛的关注。SiC 材料具有 3 倍于硅材料的禁带宽度,10 倍于硅材料的临界击穿电场强度,3 倍于硅材料的热导率,因此 SiC 功率器件适合于高频、高压、高温等应用场合,且有助于电力电子系统的效率和功率密度的提升。

自2001 年Infineon推出第一款商业SiC 二极管以来,SiC 器件的研究已经得到了极大的发展,国内外都有不少研究成果。SiC 结型场效应晶体管(junction field effect transistor,JFET)器件、MOSFET器件的研发也逐步从科研机构向企业转移。JFET器件及 MOSFET 器件为单极型器件,其开关速度高,主要适用于 0.6~10kV 的范围,BJT、IGBT、门极可断晶闸管(gate turn-off thyristor,GTO)器件为双极型器件,适用于 4.5~10kV 以上的高压范围。2008 年 Semisouth 发布了第一款常关型的 SiC JFET器件,TranSiC 发布了 SiC BJT。Infineon 也在 2012年发布了第一款 SiC 开关器件产品 JFET 器件。随着工艺技术的发展和栅氧界面处理技术的成熟,2010 年 Cree 和 Rohm 推出了平面栅 MOSFET 产品,2015 年 Rohm 继续优化推出了沟槽栅MOSFETInfineon 也于 2017 年发布了沟槽栅MOSFET。

本文对近年的研究成果进行分类梳理,并进行对比分析。主要分为 SiC 二极管、SiC JFET、SiCMOSFET、SiC IGBT、SiC GTO 器件,并分析各器件在实际应用中的优势和不足。最后,本文还对现有器件技术进行总结,并对未来的发展方向进行展望。

1 SiC 功率器件

1.1 二极管

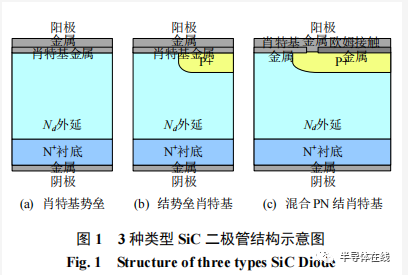

SiC 功率二极管有 3 种类型:PiN 二极管、肖特基二极管(Schottky barrier diode,SBD)和结势垒肖特基二极管(junction barrier Schottky diode,JBS),3 种类型的二极管结构如图 1 所示。JBS 二极管结合了肖特基二极管在正向导通情况下单极型导电的优点及 PiN 结二极管反向漏电流较低的优点,在4.5kV 阻断电压以下通常采用此结构。2001 年第一款商业化 SiC JBS 二极管进入市场,目前国外厂商Cree、ST 及 Infineon 公司都已推出了 0.6~1.7kV 的SiC JBS 二极管产品,最大电流为 50A,Rohm 采用推出了 0.6~1.2kV 的 SBD 二极管产品,最大电流为40A。

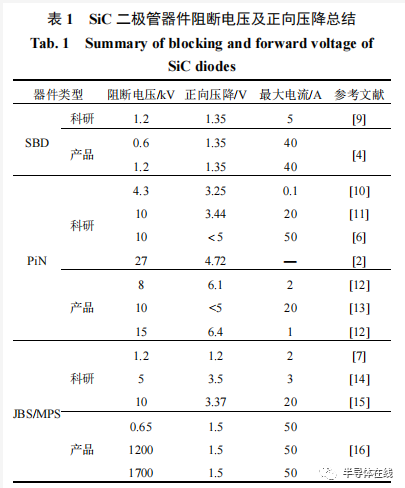

随着器件耐压的进一步提高(4.5~10kV 以上),漂移区的电阻增加,限制了单极型器件性能的进一步提高,因此相比于肖特基二极管 PiN 结二极管在高压场合更具优势。京都大学于 2012 年完成了26.9kV SiC PiN 二极管的研制,其比导通电阻低至9.7mΩ.cm2。GeneSiC 公司推出了 8kV/2A 以及15kV/1A 的 PiN 二极管产品,但是其电流能力远低于直流输电等高压应用场合的需求。大电流能力就需要大面积的器件,但是 SiC 厚外延生长工艺会引入的额外的缺陷密度会导致 PiN 二极管的良率较低限制大面积芯片的商业化。2005 年 Cree 研制了10kV/50A 的 SiC PiN 二极管,但良率仅有 23%。此外 SiC 材料中少子寿命较短,双极型电导调制效应不显著,使得 PiN 二极管的器件的导通电阻较大,因而开发成熟的提高少数载流子寿命的工艺成为研发高压大电流 PiN 二极管器件的另一个关键点。表 1 总结了现有 SiC 二极管的电压等级和器件性能。

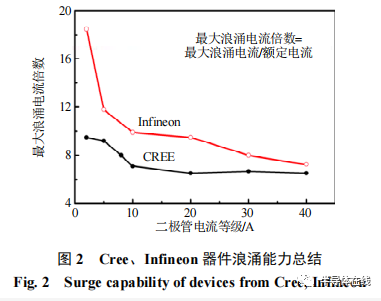

目前 SiC 二极管已大量运用于商业化的电能转换装置中。在高压大容量装置在启动的过程中,存在大电流冲击过程,该应用对二极管的抗浪涌冲击能力提出了挑战。混合 PN 结肖特基二极管(mergedPiN Schottky diode)是在 JBS 二极管的基础上提出的优化结构,通过加入大面积 P 区以及 P 型欧姆接触的设计,可以将浪涌电流能力提高 2~4 倍。通过设计以及工艺上的改进,各厂家二极管的浪涌能力普遍达到额定电流的 10 倍以上。而 Infineon通过元胞优化,其浪涌电流密度达到了 5600A/cm2的水平,为额定电流的 18 倍。Cree 和 Infineon 公司的 1.2kV 二极管产品的抗浪涌电流能力的数据如图 2 所示。

近几年来,国内 SiC 二极管产业也日益成熟,2014年起逐渐打破了国外对SiC二极管技术的商业垄断,泰科天润公司目前实现了 0.6~1.7kV 不同系列的 SiC 二极管产品的商业化。株洲中车时代电气公司发布了 0.65~5kV 不同电压等级的 SiC 二极管产品。中国电子科技集团公司五十五所建立了4~6 英寸 SiC 二极管产线,开发了 0.6~6.5kV 系列产品,单芯片导通电流最大达到 50A,同时实现了 10kV SiC JBS 二极管的研制;基本半导体公司已推出 0.65~1.7kV 不同系列的 SiC 二极管产品,电流最大可到 40A。各科研院所中,西安电子科技大学研制出了 1.2kV SiC JBS 二极管;浙江大学团队研发了 6.5kV SiC JBS 二极管、1.2kV 沟槽型JBS 二极管和 MPS 二极管,对于 MPS 二极管,通过离子注入工艺和结构设计的改进,将二极管的浪涌电流提高到额定电流的 33~35 倍,超出Infineon 第五代二极管产品的 10 倍以上。在 PiN 二极管器件方面,基本半导体推出了 10kV/2A 的器件产品,填补了国内商业 PiN 二极管产品的空白。国内 3.3kV 以下电压等级的器件与国外的器件差距逐渐减小,高压器件因受限于材料的发展水平相对比较落后。

1.2 SiC JFET

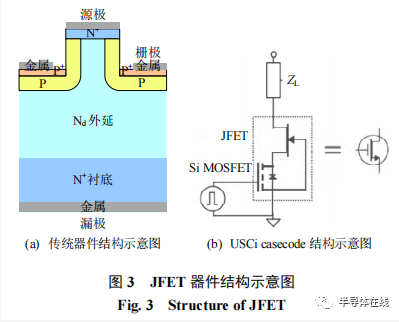

SiC JFET 器件利用栅极 PN 结耗尽层实现开关控制,同时正常状态下单极性导电,器件拥有良好的高频特性。其一种形式的器件结构如图 3(a)所示,其阈值电压通过顶部 SiC 宽度以及两侧注入的 P 区决定。2008 年美国 SemiSouth 公司发布了第一款常闭型 JFET 之后,同年罗格斯大学报道了击穿为1.65kV、比导通电阻为 1.88mΩ.cm 2 的常通型 SiCTI-JFET 器件,2009 年 Sheridan 研制了 1.9kV 的常闭型 SiC JFET 器件,比导通电阻为 2.8mΩ.cm 2。国内研究 SiC JFET 器件的公司以及研究机构较少。中国电子科技集团公司五十五所利用自主生产的SiC 外延材料,研制出 1.2~4.5kV 常关型 SiC JFET,最大单芯片电流容量达 25A。浙江大学研制出4.5kV SiC JFET 器件,正向电流达到 2.8A。

相比 MOSFET 器件来说,SiC JFET 利用 PN结控制栅极,为避免栅极 PN 结开通,栅极偏置一般不超过 2.6V。而常闭型 SiC JFET 器件的阈值电压一般在 0.7~1V,导致了两个使用和驱动方面的问题。其一是阈值电压较低,零偏关断的动态过程中容易引发误开通,其二是 2.6V 的驱动上限严重限制了器件栅极的过驱动电压,因此限制了其性能的发挥。而常通型 SiC JFET 在器件阻断时则需要施加较大的负向偏置使得沟道区域完全夹断。因此这2 种 SiC JFET 器件都无法与现有的器件(MOSFET\IGBT)的驱动电路兼容,增加了 SiC JFET 器件的使用难度。Semisouth 公司是第一家发布 SiC JFET 器件产品,但在 2013 年,因为驱动电路与硅基 IGBT器件的不兼容以及 SiC 器件市场还未打开等原因导致该公司倒闭。USCi 公司为了解决驱动不兼容的问题提出了源级级联 JFET 技术,如图 3(b)所示,器件结构使用了低压硅基 MOSFET 和 SiC JFET 级联的办法,使得器件的驱动可以与 Si 基 MOSFET\IGBT 器件兼容。至今 USCi 公司基于该级联 JFET技术推出了 650V/≤85A 及 1.2kV//≤ 63A 等不同容量的器件产品。该级联技术仍存在一些问题,包括门极驱动电路对于开关速度的控制能力降低,电路设计者无法通过改变驱动来控制开关快慢;多芯片封装带来的成本和复杂性问题、两个器件之间动态性能匹配可能带来的可靠性问题及动态开关过程中引线电感带来的损耗和可靠性问题等。

1.3 SiC MOSFET

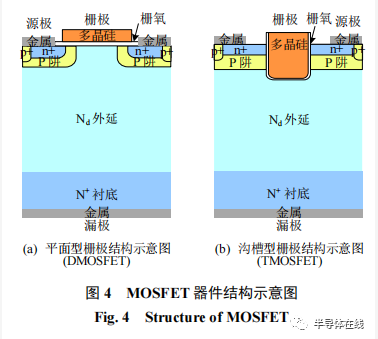

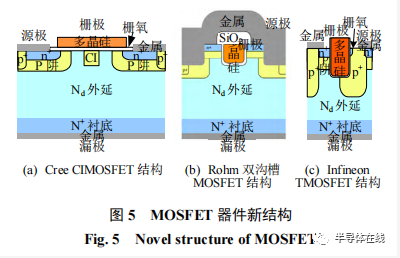

SiC MOSFET 是一种具有绝缘栅结构的单极性器件,关断过程不存在拖尾电流,降低了开关损耗,进而减小散热器体积;并且其开关速度快,开关频率高,有利于减小变换器中电感和电容的体积,提高装置的功率密度,有效降低装置的系统成本。然而器件因为在栅氧界面会引入碳团簇,引起栅氧界面态密度较高,导致沟道电阻大。针对栅氧界面,国际上众多团队在二十多年的时间中进行了大量实验,2000 年 Chung 等人报道了通过一氧化氮(NO)退火的方式将沟道迁移率提高至接近 20cm2 /Vs 的方案,栅氧可靠性也因为界面态的钝化工艺而得到了提升。随着栅氧工艺的日益成熟,2010 年起各公司相继推出 SiC MOSFET 产品。Cree 公司采用双注入 MOSFET(double implantation MOSFET,DMOSFET)的技术路线,结构如图 4(a)所示,该公司自 2010 年起发布商业化 SiC MOSFET。器件通过改进元胞尺寸以及改善 SiC/SiO2(二氧化硅)界面特性的手段,元胞尺寸从发布的第一代产品的10μm 降低至第三代产品的 6μm,比导通电阻也从发布的第一代产品的 12mΩ.cm 2 降至第三代产品的3.78mΩ.cm 2。2015 年 Cree 公司提出中心注入MOSFET(central implant MOSFET,CIMOSFET)结构如图 5(a)所示,通过在栅极下方 JFET 区域注入 P 型掺杂,减小了 JFET 区域的同时,也减小了栅氧区域的电场,其 1.2kV 器件室温比导通电阻为2.7mΩ.cm2,150℃时的比导通电阻为 3.9mΩ.cm 2。

由于 DMOSFET 结构的沟道形成于(0001)晶面上,沟道迁移率较低,同时 DMOSFET 结构还存在JFET 区域,导致器件的导通电阻很难得到进一步降低。沟槽型 MOSFET(trench MOSFET,TMOSFET)结构通过在沟槽侧壁形成沟道,不仅可以提高沟道迁移率,还能消除 JFET 区域,实现降低器件导通电阻的目的。并且由于碳化硅材料本身的特性,沟槽侧壁方向上的迁移率高于 DMOSFET 器件水平方向的迁移率,使沟槽型 MOSFET 器件的沟道电阻低于 DMOSFET。

TMOSFET 器件结构如图 4(b)所示,其正向导通电阻更小,目前业界研究热点已逐步转向TMOSFET。然而 TMOSFET 器件的沟槽角落的栅氧需要承受较大的电场强度,对器件可靠性带来隐患,如何降低了沟槽底部氧化层电场强度成为研究团队和企业研究的焦点。2012 年,日本 Rohm 公司提出了使用双沟槽结构,采用 P 型基区采用深槽刻蚀和离子注入的方法形成深 P+区,用以保护栅极氧化层的电场,如图 5(b)所示。该器件耐压达1.26kV,比导通电阻达到 1.41mΩ.cm 2。同年,日本高技术研究院(AIST)的 Okumura 在 Rohm 公司提出的双沟槽的结构的基础上,栅极沟槽底部注入P+区域。注入的 P 区降低了氧化层的电场,其击穿电压达到 3.3kV,比导通电阻达到 7mΩ.cm 2。2016年,日本 AIST 研究所开发高能注入工艺,在器件源区进行高能离子注入,加强 P 阱区域对于沟槽底部保护,制备得到的器件击穿电压达到 3.8kV,比导通电阻仅为 9.4mΩ.cm 2。2017 年,Infineon 发布了 SiC MOSFET 产品 CoolSiC™,结构如图 5(c)所示[6]。该结构以牺牲一半沟道宽度的条件下,通过深注入 P+区域更好的保护栅氧,使其不受到高电场的影响提高了器件的可靠性。

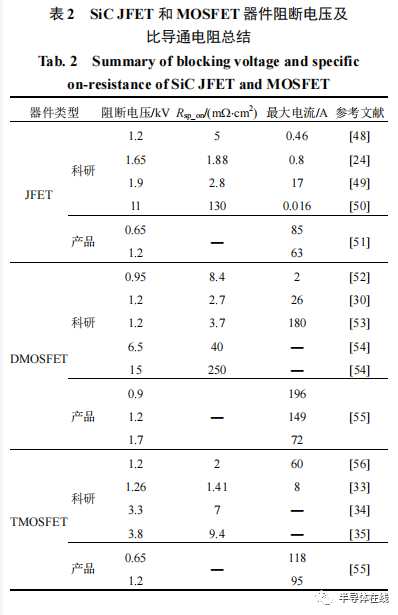

2018 年瀚薪公司将肖特基二极管集成到MOSFET 结构中代替原有 PiN 体二极管,提高了器件体二极管导通能力,并且避免了少子复合而造成的产生基平面缺陷的风险[36]。随着技术的成熟,国外产业界已逐步推出大电流的 MOSFET 器件,Rohm公司发布650V/≤118A,1.2kV/≤95A的器件。Cree 公司推出了最大电流分别为 900V/≤ 196A,1.2kV/≤ 149A,1.7kV/≤ 72A 的器件。3.3kV 及以上电压等级的器件暂时还未推出成熟的产品,仍然在进行研发工作。ABB 公司完成了 3.3kV/100A 的SiC MOSFET 器件的研制。Cree 公司推出了3.3kV/45A 的,并逐步推向市场,Mitsubishi 报道了 6.5kV/45A 的 SiC MOSFET 器件。3.3~6.5kV的器件主要针对风力发电以及高铁的应用场合,然而器件的容量只能满足风力发电的需求,但对高铁的容量需求仍有差距。而在高压 MOSFET 方面 Cree公司技术较为领先相继推出了 15kV/8A、10kV/10A以及 10kV/20A 的器件,但电流等级较实际应用环境如直流输电等仍有较大的差距。究其原因主要在于:1)高耐压器件由于外延较厚,在生长工艺中更易引入缺陷;2)MOSFET 器件栅氧部位对缺陷较为敏感可靠性存在问题。表 2 是近期 SiC JFET和 MOSFET 器件特性的总结。在 MOSFET 器件中DMOSFET 能避免沟槽角落电场聚集的问题,因而适合高压的环境,而 TMOSFET 减小了 JFET 区域的电阻且沟道电阻也能适当减小,更适合低压的环境。JFET 器件导通特性优于 MOSFET,但存在难以控制的问题。

国内 SiC MOSFET 起步较晚,中国电子科技集团公司五十五所建立了国内领先水平的高压大电流 SiC MOSFET 器件研发平台,实现了 1.2kV/50A、1.7kV/50A、3.3kV/30A、6.5kV/25A 等器件的研制,其中 1.2kV/50A 的器件比导通电阻降低至6.4mΩ.cm2,1.7kV/50A 的器件比导通电阻达到19.7mΩ.cm2,株洲中车时代电气公司完成了600V/5A、1.2kV/20A 和 1.7kV/5A 等器件的研制。基本半导体公司发布了 1.2kV/100A 的 SiC MOSFET器件。另外,中国科学院微电子所成功研制1.2kV SiC MOSFET 器件;浙江大学成功研制 1.2kVSiC MOSFET 器件,元胞尺寸为 14μm,比导通电阻为 8mΩ.cm2。

总体上,国际上多家企业已经实现 SiCMOSFET 器件的商业化,并已逐步推出沟槽型 SiCMOSFET 器件。而国内的 SiC MOSFET 器件基本采用平面栅 MOSFET 结构,研发进度相对落后,工艺技术的不成熟与器件可靠性是国内 SiC MOSFET器件的主要问题。

1.4 SiC IGBT

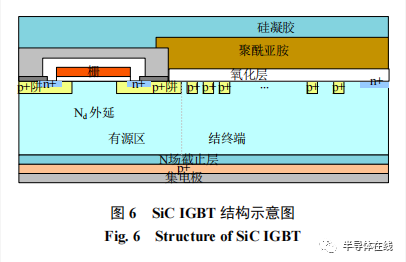

在高压器件中为了达到更高的开关速度,一般采用绝缘栅双极型晶体管(insulated gate bipolar transistor,IGBT)。IGBT 器件与 MOSFET 器件相比需要将 MOSFET 结构中的 N 型衬底用 P 型代替,正面有源区结构和工艺和 MOSFET 器件相类似,如图 6所示。2014 年 AIST 最先制作注入增强型n-IGBT,其电流达到 20A,阻断电压达到 16kV。

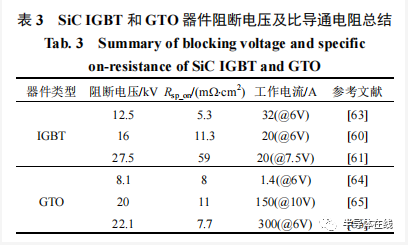

栅极偏压为 30V 的情况下,20A 时正向压降为6.35V,比导通电阻为 14mΩ.cm2。2015 年 Cree公司制作了 27.5kV 的 IGBT,器件通过热氧工艺预处理 SiC 外延片,将外延的寿命从 2μs 提高到 10μs,降低了漂移区电阻,提高了器件导通能力。栅极偏压为 20V 的情况下,20A 时正向压降为 11.7V,同时器件为正温度系数,便于器件的并联。2017年伦斯特理工学院报道了双向的 IGBT 器件。器件通过在背部制作栅氧及沟道结构,使得器件变成了两个 IGBT 器件反向并联的状态,50A/cm2 时正向压降为 9.7V,并且耐压达到 7.2kV。上述三个器件的特性总结在表 3 中,可以发现如今 SiC-IGBT器件最大电流在 32A,还是不能满足高压直流输电电流等级高于 100A 的需求。

1.5 SiC GTO

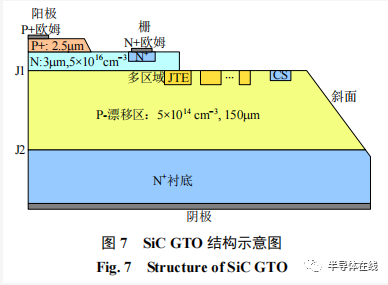

在高压器件中 IGBT 拥有较好开关速度,但是由于栅氧结构的存在,在制作大电流器件时不可避免地存在良率低,可靠性差的情况。栅极可关断晶体管(gate turn-off thyristor,GTO)可以避免这个问题。GTO 器件由于可以从阳极和阴极两侧同时注入少子,因此可以得到更高的电流密度,结构如图 7所示。2012 年 Cree 公司研制 GTO 其耐压达到22.1kV。2015 年北卡州立大学研制出首个正反向阻断耐压对称且都达到 4kV 的 GTO 器件。

表 3 是 SiC GTO 和 IGBT 器件特性的总结,因为不存在栅氧结构,GTO 器件已实现的通流能力大于 IGBT 器件,但仍低于直流输电等场合的容量需求。SiC IGBT 和 GTO 器件两者都处于研发的阶段,离成熟的技术、稳定的工艺、可靠的性能以及产业化还存在较大的差距。

1.6 器件特性总结

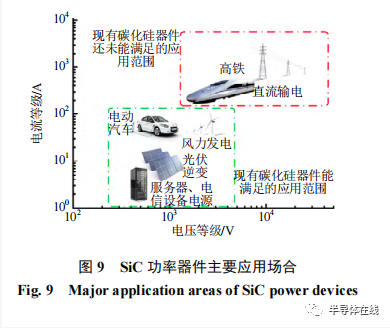

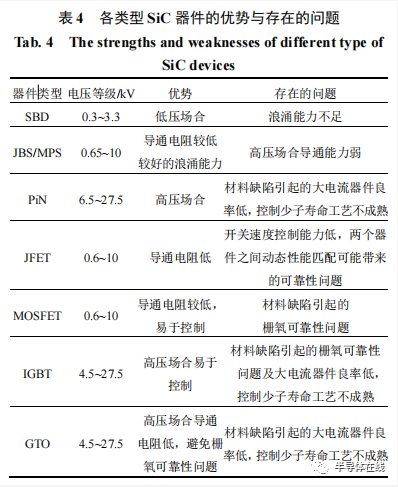

前文论述了各类器件的特性和发展历史,图 8展示了目前已报道的 SiC 各类型器件的阻断电压和比导通电阻的分布情况。在实际碳化硅的应用场合如图 9 所示:光伏逆变模块主要使用 0.6~1.2kV,电流等级在 20A 以上的器件;电动汽车模块主要使用 0.6~1.2kV,电流等级在 20~50A 的器件;风力发电主要使用 1.2~3.3kV,电流等级高于 20A 的器件;高铁应用场合中则需要 3.3~6.5kV,电流不低于100A 的器件;直流输电的应用场合中需要大于6.5kV 电压等级且导通电流大于 100A 的器件。具体各类器件的优势和不足在表 4 中列出。

现阶段在SiC 二极管器件中,0.65~1.7kV 的 JBS 器件较为成熟,能提供超过 100A 电流的单管芯片,满足光伏逆变、电动汽车以及风力发电场合的应用。在高压大电流器件方面,由于材料和工艺的原因,PiN 二极管器件仍然距离市场化较远,需通过生长缺陷密度更低的碳化硅外延材料以及开发成熟的增强寿命的工艺以满足实际应用场合大电流的需求。在开关器件中,JFET 器件较为特殊,一般使用 USCi 公司的级联结构,其特性与 MOSFET 相类似,但驱动对开关速度等参数的控制能力削弱。MOSFET 器件中 0.65~1.7kV 电压等级的器件也逐步推向市场,逐步在光伏逆变、风力发电中应用,其栅氧工艺也在逐步完善。国外厂家的 MOSFET 器件都已陆续通过可靠性检验,并使用在电动汽车等应用上。但是在高铁等大功率,高可靠性的应用场景,器件还存在提升空间。而直流输电等超高压大电流的工作状态需要 IGBT 器件和 GTO 器件,GTO 器件能避免栅极氧化层带来的可靠性问题而更被看好,而如何降低器件材料的缺陷,增加器件的电流能力则是两类器件都亟待解决的问题。

2 SiC 器件技术展望

SiC 二极管以及 SiC MOSFET 已逐步走向市场,出现较为成熟的产品。SiC 二极管因为不存在反向恢复电荷的优点,已逐步替代硅基二极管得到广泛的应用。SiC MOSFET 也逐步用于光伏逆变器、充电桩等实际应用场合,然而 MOSFET 器件栅氧的质量以及较高的成本仍然是限制其得到普遍应用的瓶颈。在未来 5 年内国内外的研究内容将集中在 SiC 衬底和外延质量的提升、栅氧工艺的优化和器件可靠性的提高、高压大容量 SiC 器件的研发以及超级结等新型器件结构等方面。

2.1 SiC 衬底和外延技术

SiC 材料现有外延生长工艺中会引入晶体的非理想状态,包括扩展缺陷以及点缺陷。大部分的扩展缺陷是由从衬底材料中复制而来,也有少部分在外延生长工艺中引入。而点缺陷主要由外延生长工艺引入。扩展缺陷主要包括微管(micropipe)、基平面位错(basal plane dislocation)、螺旋位错(threading screw dislocation)、刃位错(threading edge dislocation)及堆垛层错(stacking fault)。微管是最为致命的缺陷,会引起阻断电压大幅度下降以及漏电流的大幅度升高,如今外延厂商基本已将缺陷密度的控制在0.1cm-2 以下,技术较为领先的 Cree 等公司已经能生产零微管的碳化硅 4 寸晶圆。基平面位错会显著的影响少子寿命,增加导通电阻,并且由于少子复合的能量释放逐步扩展为堆垛层错,影响器件耐压,同时受该缺陷影响的面积也会增大。目前基平面位错密度基本控制在 200cm-2 左右。而螺旋位错、刃位错截至目前发现对器件影响较小,只发现局部减小双极型器件的载流子寿命的现象,目前该类缺陷密度分别在 200~500cm-2 以及 300~1000cm-2左右。而其他的一些如三角形缺陷、胡萝卜缺陷以及颗粒引入的缺陷(down-fall)会引入堆垛造成漏电流的增大以及阻断电压的降低,但此类缺陷密度较低在 0.1cm-2 左右。如今 SiC 材料对缺陷的研究仍然处于起步阶段,一方面缺陷影响器件性能的机理尚需研究;另一方面从根本上解决缺陷形成主要有

两种方案,一是在生长衬底过程中避免上述缺陷形成,二是通过调整外延的工艺,避免外延工艺受到底部衬底的干扰。两种方案都处于研究的起步阶段,还需经历大量的工艺实验和测试验证。

2.2 栅氧工艺的优化和器件可靠性的提高

MOSFET 器件栅氧的质量成为限制其应用的瓶颈。高温状态下,栅氧界面态会俘获/释放载流子,影响器件稳定性和可靠性,而评价栅氧是否能长期可靠地工作,最好的方式就是在高温环境下采用TDDB(time dependent dielectric breakdown)测试器件的寿命。1999 年 CREE 公司 Lipkin 以及 Palmour测试栅氧结构发现,在环境温度为 350℃并且施加6MV/cm 电场的情况下,栅氧的寿命只有 1000s。

2008 年,利用 NO/NO2 退火处理氧化层的方式,罗格斯大学通过 TDDB 测试发现在 375℃以及6.4MV/cm 的条件下 63%器件失效的平均时间为215h。实验数据证明栅氧可靠性得到了很大的提高。2006 年,Krishnaswami 通过 175℃环境下的TDDB 测试 2kV SiC DMOSFET,推测出在 3MV/cm的电场下寿命达到 100 年。2010 年罗格斯大学发现在高场强下氧化层击穿的模式与普通一般器件正常工作栅氧电场在3MV/cm情况下的击穿模式不一致,因而采用较低场强,较长时间的 TDDB 测试,器件通过在 300℃加 6MV/cm 方式发现器件寿命达到了 183 天,并且外推出器件在 300℃时,在 4.3MV/cm 的电场强度下,寿命可达 100 年。2016 年中科院微电子所提出采用氮氢混合气氛对栅氧进行处理得到的氧化层击穿电荷增加至 0.078C/cm2。目前 SiC MOSFET 器件栅氧工艺的水平仍然没有达到 Si MOSFET 器件栅氧工艺的成熟度,阻碍了SiC MOSFET 器件的性能的进一步提升和可靠性的提高,未来还需更多研究工作,探明栅氧界面态的形成机理和抑制方法,从而提高 SiC MOSFET 器件的性能与可靠性。

2.3 高压大电流的大容量 SiC 器件

现在的商业 SiC 管主要集中在 0.9~3.3kV,并出现部分 6.5kV 的产品。然而 10kV 及以上的器件仍然处在研究和技术储备阶段。主要难点在于:

1)衬底的质量不够理想,衬底的缺陷密度水平很大程度上决定了厚外延层的质量,目前衬底的缺陷密度仍然有待进一步降低;2)厚外延生长仍然是挑战,外延生长过程中会引入新的缺陷,外延工艺仍需要进一步优化降低新引入的缺陷密度,同时也需要寻找新技术降低衬底缺陷对外延质量的影响;3)高耐压器件终端设计较为复杂,使用场限环效率较低消耗的面积大,因而需要采用结终端扩展以及斜角等新型终端设计,减小面积,使得器件性能得到提升。

2.4 SiC 超级结器件

在硅器件中由于超级结器件结构的提出,使得器件性能突破了一维的单极型理论极限,性能优异。SiC 超级结器件也与硅超级结器件一样具备优异的特性。制作 SiC 超级结器件主要有以下几种方式:1)沟槽型超级结器件,此结构最早由浙江大学提出并制作肖特基二极管,阻断电压达到1.35kV,比导通电阻为 0.92mΩ.cm 2(去掉衬底电阻为 0.36mΩ.cm 2)。该工艺难点在沟槽刻蚀形貌,以及沟槽的回填。2)沟槽回填型超级结器件,此工艺方式由日本先进科技产业研究院提出并制作[74],该方式对沟槽刻蚀工艺以及外延回填工艺有较高的要求。该工艺制作的 MOSFET 器件阻断电压达到 7.8kV,比导通电阻仅为 17.8mΩ.cm 2。3)多次注入–外延形成的超级结器件,此工艺方式较为复杂,但避免了在高深宽比沟槽中的外延工艺,只需在水平表面生长外延。研制的 MOSFET 器件性能达到 1.62kV,比导通电阻仅为 2.7mΩ.cm 2。总体来看,现有 3 种制作超级结器件的工艺,只有浙江大学的工艺方式不依赖于外延生长工艺,但该方式会牺牲部分器件性能。而日本研究组提出的两种方式对外延生长工艺要求较高,制作的器件性能也更优异。针对 SiC 超级结器件的研究目前还在起步阶段,如何系统揭示 SiC 超级结器件和浮空结器件中漂移区和终端区域空间电荷分布方式对其电场分布的影响机理和优化方法还未探明;如何获得具有理想形貌的高深宽比高密度 SiC 沟槽还需尝试;以及如何探明在超级结器件深沟槽区域和浮空结器件离子注入区域外延再生长过程中的晶体生长动力学机理和缺陷形成机制还需要进行研究。

3 结论

本文就 SiC 器件结构发展历史入手,介绍了产业界器件发展历史,并就 SiC 各类器件的特点进行总结,对各类器件结构和工艺的优化进行报道。通过上述器件类型的对比,在 5~10kV 以下 JFET 和TMOSFET 的静态性能较为优异,但 JFET 驱动较为复杂,而 TMOSFET 为较新的技术,其技术成熟度相对较低。另一方面,DMOSFET 静态性能相对较劣,但其技术成熟度较高。在 5~10kV 以上主要使用 IGBT 和 GTO 器件,IGBT 器件开关速度较快,驱动较为方便。GTO 器件驱动相对复杂,但是电流承载及过流能力强。当前,SiC IGBT 和 GTO 器件技术离产业化和大规模使用都还有较大差距,存在较好的潜力和研究价值。针对碳化硅材料的缺陷研究还在起步阶段,如何抑制缺陷对器件尤其是高压大电流器件生产的良率起到至关重要的作用。除此之外,碳化硅超级结器件技术有望突破一维单极性器件的性能极限,但是该技术仍处于起步阶段,未来还需投入更多的研究。

可以看见,碳化硅器件的发展已经为电力电子技术打开了一扇更广阔的大门,碳化硅器件技术的逐步发展将助力于电力电子技术朝着高频、高效、高功率密度的方向前进。

来源:中国电机工程学报第40卷 第6期

作者:盛况、任娜、徐弘毅 (浙江大学电气工程学院)