近日,以“创芯生态 碳索未来”为主题的第七届国际第三代半导体论坛暨第十八届中国国际半导体照明论坛(IFWS & SSLCHINA 2021)在深圳会展中心举行。本届论坛由第三代半导体产业技术创新战略联盟(CASA)、国家半导体照明工程研发及产业联盟(CSA)联合主办,北京麦肯桥新材料生产力促进中心有限公司与半导体产业网共同承办。

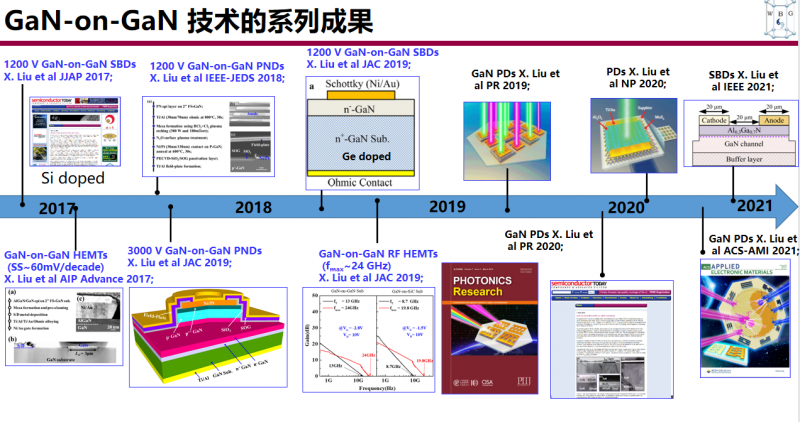

氮化镓材料具有高频、高效、高功率、耐高压、等优越性能;切合国家“新基建”的国家战略需求,是重点核心材料和电子元器件;也是解决高科技卡脖子问题的重要方向。期间,“氮化镓功率器件“专场上,深圳大学微电子研究院院长助理、材料学院研究员刘新科做了题为”2寸独立晶圆上1.7 kV垂直GaN-on-GaN肖特基势垒二极管“的主题报告,GaN-on-GaN技术路线的独特特点包括缺陷密度极低(约103cm-2; 横行器件和纵向器件; 相同器件面积下,更大的电流和更高的耐压;超强的器件可靠性,无电流崩塌等。报告从终端结构设计、GaN-on-GaN 材料分析;GaN-on-GaN 器件制备:He离子注入终端;GaN-on-GaN SBD器件性能等角度分享了最新研究进展。

其中,GaN-on-GaN SBDs方面,通过HVPE+MOCVD混合生产方法,优化漂移层背景电子浓度 (5E18cm-3), 实现了高质量2寸氮化镓单晶衬底外延片。采用无金硅基CMOS兼容技术制备的GaN器件技术,为GaN功率器件的量产提供了一种有效的技术路线。创新采用Ge掺杂技术实现了低应力单晶外延片,由于Ge原子半径更加接近Ga原子,可以降低94%的内张应力。新型保护环和场板的复合结构终端,有效降低阳极边缘的峰值,有效提高器件的耐压。

GaN-on-GaN PND方面,采用HVPE+MOCVD混合生产方法,实现了高质量2寸氮化镓单晶衬底外延片;采用无金硅基CMOS兼容技术制备的GaN器件技术,为GaN功率器件的量产提供了一种有效的技术路线。创新采用Ge掺杂技术实现了低应力单晶外延片,由于Ge原子半径更加接近Ga原子,可以降低94%的内张应力。新型保护环和场板的复合结构终端,有效降低阳极边缘的峰值,有效提高器件的耐压。

GaN-on-GaN PNDs方面,创新采用O掺杂技术实现低电阻率衬底,为实现氮化镓理想功率器件的品质因子更进一步;低损伤刻蚀技术和无损伤的旋装玻璃镀膜技术,实现金属场板的终端结构,有效降低阳极边缘的峰值。

刘新科,深圳大学教授,长期从事宽禁带氮化镓以及氮化镓异质结的半导体器件研究,在Adv. Mater., Adv.Funct.Mater., Adv. Electron. Mater. IEEE EDL, IEEE TED,APL等知名期刊发表第一或通信作者SCI收录论文80篇,申请专利50项,授权专利9项(含3项PCT和1项美国专利), 科研成果被Semiconductor Today,MaterialsviewChina多次报道,科研成果被Photonic Research 和Advanced Electronic Materials选为封面文章。目前承担国家科技部重点研发计划课题和任务各一项、国家自然科学青年和面上科学基金各一项、广东省科技计划项目一项、广东省重点研发计划课题三项,深圳市基础研究布局一项、深圳市技术攻关一项等10多项科研项目。

(内容根据现场资料整理,如有出入敬请谅解)