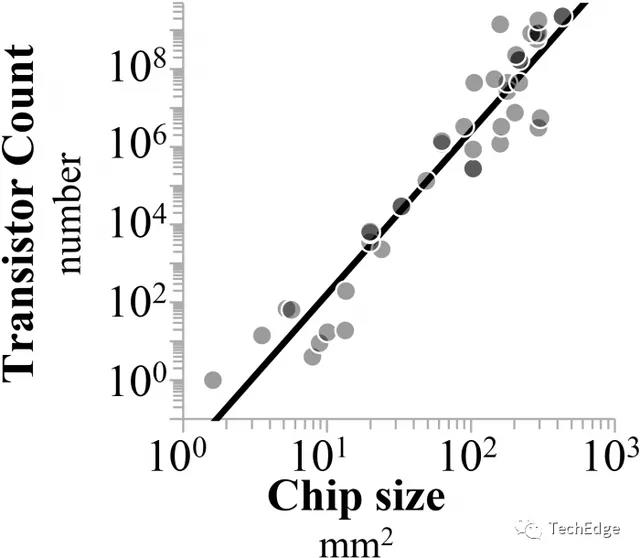

随着芯片制程工艺缩进难度的日渐提升,想要实现集成电路组件数量每两年翻一番的目标,似乎已经遇到了瓶颈。然而洛克菲勒大学的一支研究团队,刚刚对影响半导体行业数十年的“摩尔定律”有了新的认识。在《PLOS One》期刊上的一篇文章中,其揭示了一种更微妙的“历史波动”模式 —— 即硅芯片晶体管密度的上升,使计算机和其它高科技设备变得更快、更强大。

事实上,自 1959 年以来,半导体行业已经历六次这样的改进浪潮,且每次持续大约 6 个年头。

洛克菲勒大学研究团队在《通过英特尔芯片密度重新审视摩尔定律》一文中指出:在每一轮周期中,芯片的晶体管密度都至少增加了 10 倍。

SCI Tech Daily 指出,该论文建立在将早期 DRAM 芯片作为研究技术进化模式的研究基础之上、但排除了 1959 年开始在仙童和英特尔处理器上不断变化的芯片尺寸等因素,从而描绘出了一条更加简洁直观的波形弧线。

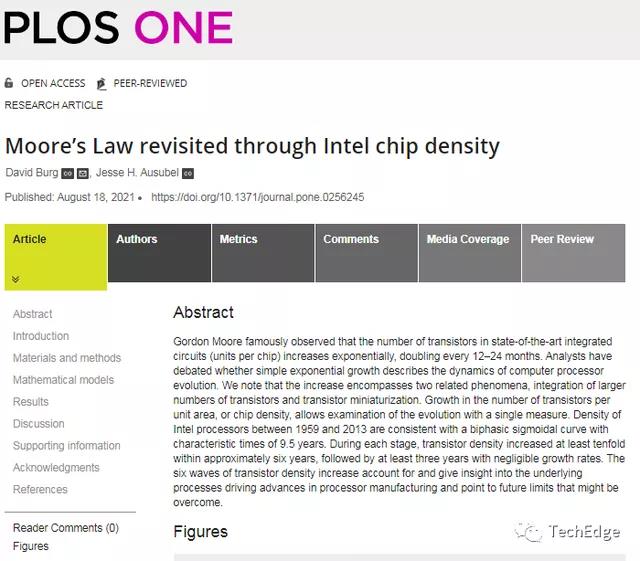

研究配图 - 1:时间相关逻辑模型 / 半对数变换曲线

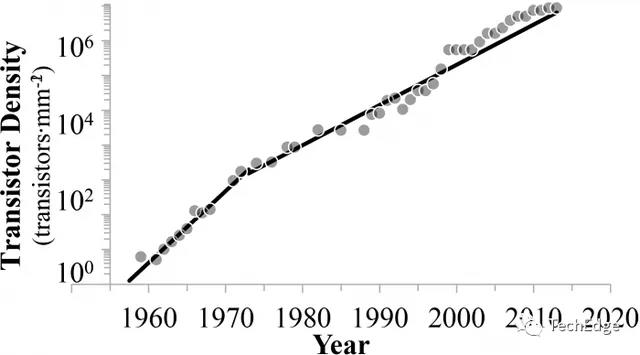

研究作者、纽约洛克菲勒大学人类环境项目(PHE)成员的 Jesse Ausubel 和 David Burg 表示:在每 6 年的增长浪潮之后,大约有 3 年的增长可以忽略不计。

此外他们认为,在面部识别、5G 移动网络和相关设备、自动驾驶、以及需要更高处理速度和算力的人工智能(AI)和机器学习(ML)等高科技创新等需求的驱使下,通过晶体管小型化来推动芯片计算能力的下一波增长的设想,也已经过时了。

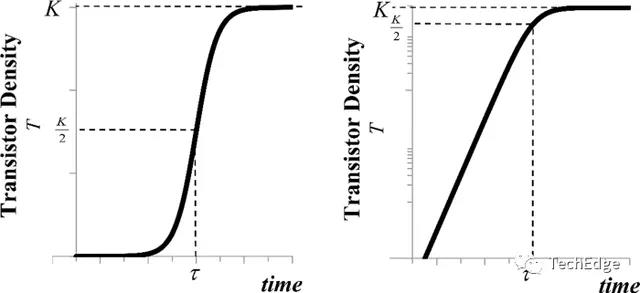

有趣的是,一家名叫 Cerebras 的初创企业,刚刚吹嘘其打造的有史以来最大的晶圆级芯片(Wafer-Scale Engine),可知其大小为市面上最大的图形处理器(GPU)的 56 倍。

研究配图 - 2:最先进处理器尺寸与晶体管数量的幂律关系

这款晶圆级芯片拥有总计 1.2 万亿个晶体管,嵌入了 40 多万个 AI 优化核心(是市面最大 GPU 的 78 倍),辅以 3000 倍的片内缓存。

然而受物理现实和经济因素的限制,硅芯片的高速发展时代,或在仅剩的一两次冲锋后就偃旗息鼓。

因为计算机行业的持续增长,将取决于纳米晶体管、单原子晶体管、以及量子计算小型化等方面的创新。

研究配图 - 3:最先进集成电路密度的逐年发展(单位:m㎡)

论文指出,早在 2019 年,Google 母公司 Alphabet 就宣称在量子计算方面取得了突破,其名为“Sycamore”的可编程超算处理器用上了可编程的超导量子比特。

由该公司发布的基准测试示例报告可知,Sycamore 在大约 200 秒内完成了一项任务。但若使用当时最先进的传统超算,将需要耗费大约 10000 年的时间。

PHE 主管 Jesse Ausubel 称:“我们已经在硅基芯片上实现了六次飞越,但最终可能转向其它材料和工艺方案,量子比特有望终结我们在现阶段的艰难攀越”。

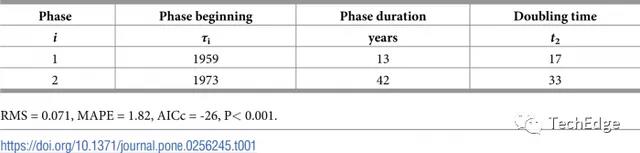

研究配图 - 4:逐步指数模型的参数值

有关这项研究的详情,已经发表在近日出版的《PLOS One》 期刊上,原标题为《Moore’s Law revisited through Intel chip density》。