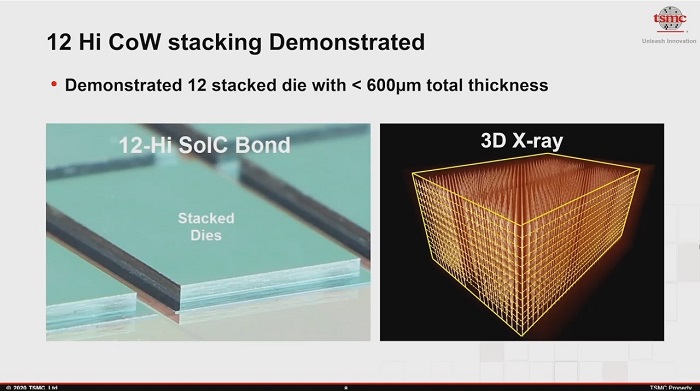

资料图(来自:TSMC)

近年来,随着芯片制程缩减的减速,制造商开始依托于更加高级的堆叠、互连和封装技术。此外在从水平向 3D 堆叠推进的同时,芯片的功耗、散热和设计复杂度也在飞速提升。在本周的技术研讨会上,台积电(TSMC)就介绍了该公司对于未来的最新展望。据悉,该公司将大力推进 SoIC 集成芯片系统的发展。

由台积电分享的一张幻灯片可知,这项关键技术的复杂度,远超以往的硅中介层或芯片堆叠工艺。因其允许在不使用任何 μ-bumps 凸点的情况下堆叠硅芯片,而是直接将金属层彼此对准并键合到硅片上。

目前台积电正在积极探索12-Hi 配置的 SoIC 方案,每个管芯都有一系列的硅通孔(TSV),以便每层与其它层进行通信。其设计理念是每层都可具有不同的逻辑元素,比如 IO 或 SRAM 。

此外某层也可以是无源的,以充当其它有源层之间的隔热层。如 PPT 所示,这种设计的最大厚度为 600 μm,意味着单层厚度要控制在 50 μm 以下,而传统标准管芯堆叠解决方案上的凸点间距也是 50 μm 左右。

至于 SoIC,N7 / N6 工艺下的混合键合间距为 9 μm,N5 工艺更是可以缩减到 6 μm 。这表明台积电拥有一些令人印象深刻的线性制造和晶圆减薄技术,以实现如此高水平的管芯对准与一致性。

该公司甚至展望了将之进一步缩减到 0.9 μm 的能力,以使之扩展至硅芯片的后端互连。至于最终的制造难度和客户的接纳程度,仍有待时间去检验。

来源:cnBeta.COM