近期,北京大学团队研发增强型 p 型栅氮化镓(GaN)晶体管,并首次在高达 4500V 工作电压下实现低动态电阻工作能力。

研究人员在 GaN 功率器件的表面引入新型有源钝化结构,在蓝宝石衬底成功制备具有该结构的新型器件。所制备的器件击穿电压得到大幅度提升,实现大于 6500V 的耐压能力。

通过提供低成本的增强型 GaN 功率器件解决方案,攻克了制约 GaN 功率器件近 30 年的动态电阻难题,打破了“GaN 功率器件不适用于千伏级工业电子应用”的固有观念。

图丨魏进(来源:魏进)

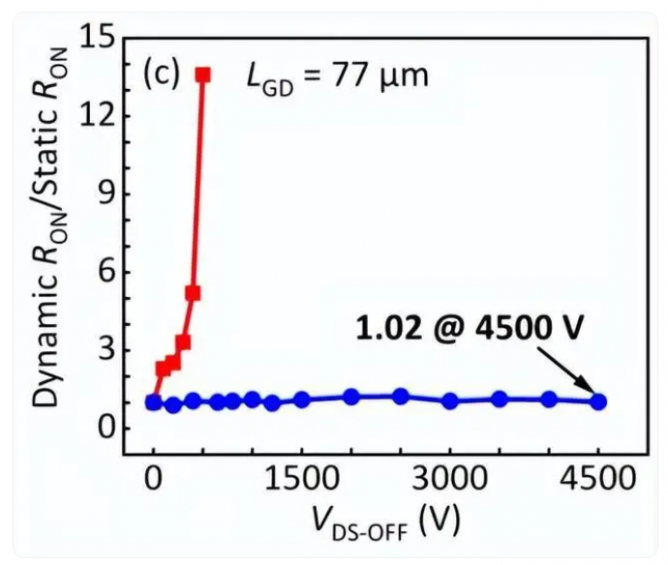

具体来说,在 4500V 工作电压下,超高压 GaN 功率器件的动态电阻退化仅为 2%。与之对比的是,同一晶圆上的传统器件在 500V 工作电压下,动态电阻退化已超过 100%。

该技术有望为新能源汽车、轨道交通、电力传输、分布式储能、清洁能源、数据中心电源等应用设备提供高效率、轻量化、小型化的能源管理系统。

图丨相关论文(来源:IEDM)

近日,相关论文发表在美国旧金山举办的 IEEE 国际电子元件会议(International Electron Devices Meeting,IEDM)上,题目为《具有超低动态电阻的 6500V 有源钝化氮化镓 p 型栅高电子迁移率晶体管》(6500-V E-mode active-passivation p-GaN gate HEMT with ultralow dynamic RON)。

北京大学博士研究生崔家玮为论文第一作者,北京大学魏进研究员、王茂俊副教授、沈波教授为论文共同通讯作者,合作单位包括清华大学、日本名古屋大学。

行业瓶颈:GaN 功率器件难以用于千伏级别电压等级

GaN 半导体材料因具备卓越的耐压与输运特性,有望推动电子设备在系统效率提升、系统微型化发展方面取得革命性进展。

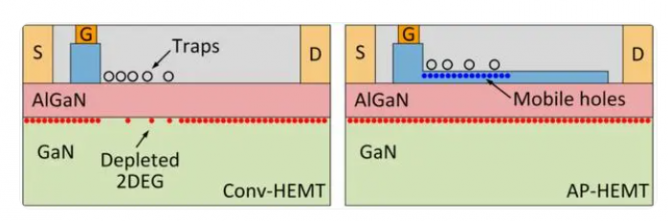

目前,GaN 功率器件的电压等级并非受限于击穿电压,而是被局限于高压工作后的动态电阻退化。动态电阻退化源于器件表面的深能级陷阱响应速度极为缓慢,一旦填充电子需要很长时间才能恢复,这些表面负电荷排斥沟道中的电子引起动态电阻退化。

同时,GaN 功率器件又依赖于表面深能级陷阱态,为导电沟道提供载流子。因此,动态电阻退化被认为是 GaN 功率器件的本征特性之一。

经历近 20 年的研究,目前业界普遍采用 3 至 4 个场板结构,可以将 650V 电压等级的 GaN 功率器件的动态电阻退化控制在可接受的程度。

然而,对于更高电压等级的器件,所需场板数量成比例增加,每增加一个场板就需要多一次光刻。若想实现 6500V 的 GaN 功率器件,则需要几十次额外的光刻,因此失去了现实意义。

有鉴于此,工业界与学术界形成普遍的共识:GaN 功率器件不适用于千伏级别的电压等级。

解决有源钝化 GaN 晶体管的三个技术难题

那么,是否有可能从根本上解决动态电阻退化的问题呢?

早在 20 年前,美国加州大学圣巴巴拉分校研究人员尝试采用一个 p 型半导体层,来屏蔽器件表面陷阱的影响,但未取得理想的结果。

魏进在香港科技大学读博时,就开始思考如何利用屏蔽效应消除表面深能级陷阱态的影响。彼时,很多国内外课题组发现 GaN 功率器件阈值电压漂移的现象,并认为这是 GaN 半导体材料缺陷引起的。

2019 年,他在研究碳化硅(SiC)功率器件时,发现在某些情况下,因为器件结构设计,会出现电荷存储现象造成器件特性漂移。因此,当产生电荷损失时,没有电荷源泉可以快速补充电荷,导致器件稳定性变差。

经过分析,魏进发现 GaN 功率器件有类似之处。“这说明 GaN 器件的阈值电压本质上是动态变化的,而非由材料缺陷所导致。”他说。

后续很长时间,魏进都在研究如何验证这一理论。他与所在团队发明了一种测试方法,对器件内部的存储电荷量与阈值电压漂移量分别测试,发现这二者完全吻合。

基于此,他们提出 GaN 功率器件动态阈值电压理论[2],让“动态阈值电压”概念成为 GaN 功率器件的普遍共识。

加入北京大学后,魏进课题组的研究方向是功率半导体器件,研究重点包括 GaN 功率器件、SiC 功率器件以及功率集成电路技术。

他和团队成员再次将注意力投入到“动态电阻退化”这个古老的方向上。之前,在动态阈值电压理论上的研究给他们提供了重要的思路。

魏进表示:“当我们再思考如何屏蔽表面深能级陷阱态时,意识到为屏蔽层提供能够快速响应的电荷源泉,是解决问题的关键。因此,我们有了这一概念的雏形。”

(来源:IEDM)

最初,该团队认为,屏蔽电荷的源泉应该是固定电位,器件中的固定电位只有器件源极,即参考电压 0V。然而,p 型屏蔽层的引入会耗尽下方的电子沟道,造成电子浓度的减少甚至消失。

因此,他们将研究重点放在怎样弥补屏蔽层下方的电子损失。魏进表示:“有一天我突然想到,屏蔽层与栅极连接可利用栅极的正电压所产生的场效应,来恢复屏蔽层下方的电子浓度。”

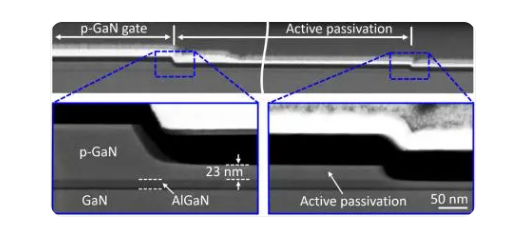

图丨在蓝宝石衬底上制备的超高压 GaN 功率器件透射电镜图像(来源:IEDM)

在零电压偏置下,有源钝化层耗尽下方的电子沟道,实现增强型工作模式。当需要器件导通时,研究人员采用一种与传统器件截然不同的方式产生电子沟道。

具体来说,传统器件利用表面深能级陷阱为沟道提供电子,而该器件则是利用栅极电压的场效应作用,重新在沟道中产生高浓度的电子。

但这时仍有一个棘手的问题:器件的耐压能力是否会受到有源钝化结构的影响?根据在 GaN p 沟道晶体管的研究经验,魏进发现,当 p 型层足够薄时可被耗尽,从而实现超高的耐压能力。

至此,有关有源钝化 GaN 晶体管的三个主要技术难题被完美解决,即如何实现低动态电阻、如何实现增强型工作模式、如何承受高压。“相关的实验结果也充分验证了我们的想法。”魏进说。

该器件展示了沟道电子的产生可以不依赖于表面深能级陷阱态,并且,表面深能级陷阱态的影响从原理上能够被完全消除。最终,该器件同时实现了三个关键特性:大于 6500V 的超高耐压、增强型工作模式以及超低动态电阻。

以低成本实现性能“飞跃”

目前,成熟的超高压功率器件是垂直型 Si 绝缘栅双极晶体管或 Si 晶闸管,但它们的开关频率非常低。一种解决方案是采用宽禁带半导体 SiC 功率器件,以大幅度提高开关频率。

但是,SiC 超高压器件需要特殊的厚外延工艺,且需要将外延材料的背景掺杂控制到极低的水平,这需要极高的成本。对于 SiC 功率器件,额外的成本还包括昂贵的衬底及特殊的高温工艺设备。

GaN 超高压器件采用与低压器件相同的外延材料、蓝宝石衬底、成熟的 Si 工艺设备。据了解,该技术采用低压器件的流程,甚至不用专门为超高压器件区开发工艺流程,仅需要修改版图设计。

据研究团队估计,在大规模量产条件下,同等电流水平的 GaN 器件的成本接近 Si 器件,但是却能带来性能上的“飞跃”。

目前,美国在 GaN 超高压器件领域投入大量研发资源,而中国在该领域的研究处于世界领先的水平。然而,中国相关配套技术的研发仍未启动。魏进表示:“希望我们的研究结果能够鼓励国内在 GaN 超高压器件的研发投入,推动配套技术从实验室进入到产品化阶段的研发。”

(来源:IEDM)

未来,功率器件的突破有望带来能源管理技术的变革。

人们可能会看到笨重的电力变电站变得更加小型化,从而能够更加灵活地在城市布局;电动汽车中体型庞大的电机驱动与充电模板变得更加小型化,进而腾出宝贵的乘用空间或安装更高容量的电池,以大幅度地提高续航里程。

功率器件的突破更有望对未来社会的组织方式产生深远的影响,使曾经受限于能源管理系统的重量与体积,以及设备的续航能力的概念性应用更快地进入实用,例如小型载人飞行器、穿戴式机械外骨骼等。

继续探索 GaN 超高压功率器件的性能边界

本届微电子器件的最高学术会议 IEDM 上,魏进课题组还另展示了两篇论文,分别是攻克 GaN 动态阈值电压漂移[3],以及在体硅衬底上实现 650V GaN 集成电路[4]。两篇论文的第一作者均为该课题组的博士生杨俊杰。

值得关注的是,在本次 IEDM 大会中,功率器件分会共 13 篇论文,其中北京大学 3 篇,这是 IEDM 大会中极为罕见的场景:中国的研究团队在微电子器件国际顶级会议一个主要的研究方向上成为主力。

图丨魏进课题组部分成员合影(来源:魏进)

后续,魏进将与团队进一步探索 GaN 超高压功率器件的性能边界,尝试通过技术创新突破一个个曾经认为的性能极限,从而展示 GaN 功率器件的巨大潜力。

据悉,研究人员已申请多项相关专利,同时也在与企业界保持沟通,探索合作开发的具体事项。与此同时,他们也将积极研究 GaN 功率器件的应用技术,与其他合作者及产业界合作,共同探究 GaN 功率器件在应用中问题,并提出相关解决方案。

该技术的提升空间仍然很大,从 GaN 半导体材料的物理特性来说,器件的击穿电压还有提升空间,导通电阻也可进一步降低。

另外,魏进课题组也在积极探索 GaN 功率集成技术[5],在同一芯片集成不同种类的器件,形成具备各种功能的智能功率集成电路,实现易用、可靠、小型化。

参考资料:

1. J. Cui, J. Wei, M. Wang, Y. Wu, J. Yang, T. Li, J. Yu, H. Yang, X. Yang, J. Wang, X. Liu, D. Ueda, and B. Shen, 6500-V E-mode active-passivation p-GaN gate HEMT with ultralow dynamic RON. IEDM, San Francisco, CA, USA, 2023, sec. 26-1.

2. J. Wei, R. Xie, H. Xu, H. Wang, Y. Wang, M. Hua, K. Zhong, G. Tang, J. He, M. Zhang, and K. J. Chen, Charge storage mechanism of drain induced dynamic threshold voltage shift in p-GaN gate HEMTs. IEEE Electron Device Letters, 40, 4, 526-529, 2019.

3. J. Yang, J. Wei, M. Wang, T. Li, J. Yu, J. Wang, and B. Shen, Simultaneously achieving large gate swing and enhanced threshold voltage stability in metal/insulator/p-GaN gate HEMT. IEDM, San Francisco, CA, USA, 2023, sec. 9-4.

4. J. Yang, J. Wei, M. Wang, M. Nuo, H. Yang, T. Li, J. Yu, X. Yang, Y. Hao, J. Wang, and B. Shen, 650-V GaN-on-Si power integration platform using virtual-body p-GaN gate HEMT to screen substrate-induced crosstalk. IEDM, San Francisco, CA, USA, 2023, sec. 9-6.

5. J. Wei, Z. Zheng, G. Tang, H. Xu, G. Lyu, L. Zhang, J. Chen, M. Hua, S. Feng, T. Chen, and K. J. Chen, GaN power integration technology and its future prospects. IEEE Transactions on Electron Devices, 2024, doi: 10.1109/TED.2023.3341053.