SiC MOSFET器件以其高压、高频、低损耗以及高温等优越性能,显着提高电力装置的效率和功率密度,是高功率电子领域的有力竞争者。目前已有多家半导体公司相继推出商用SiC MOSFET产品并得到广泛应用,在电动汽车、光伏逆变等领域逐渐开始替代Si基电力电子器件。

9月13-14日,“2021中国(南京)功率与射频半导体技术市场应用峰会(CASICON 2021)”在南京召开。本届峰会由半导体产业网、第三代半导体产业主办,并得到了南京大学、第三代半导体产业技术创新战略联盟的指导。

会上,电子科技大学教授邓小川带来了“极端应力下碳化硅功率MOSFET的动态可靠性研究”的主题报告,从SiC MOSFET器件的可靠性评估方法、短路特性、非钳位感性负载开关(UIS)特性、浪涌电流特性等角度分享了最新研究进展。

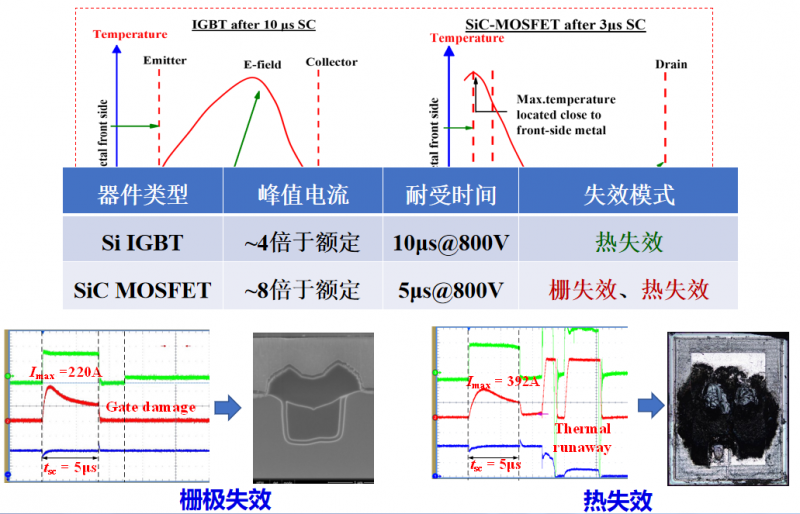

报告指出,虽然国际上SiC MOSFET器件的发展已经取得了阶段性进展,但SiC和Si材料和器件结构之间的明显差异对SiC MOSFET器件极端应力下的动态可靠性提出了挑战,已成为功率半导体器件领域的研究热点之一,其中具有代表性的动态可靠性即为非钳位感性负载开关(UIS,Unclamped Inductive Switching)特性、短路(SC,Short Circuit)特性和浪涌电流(Surge Current)特性。

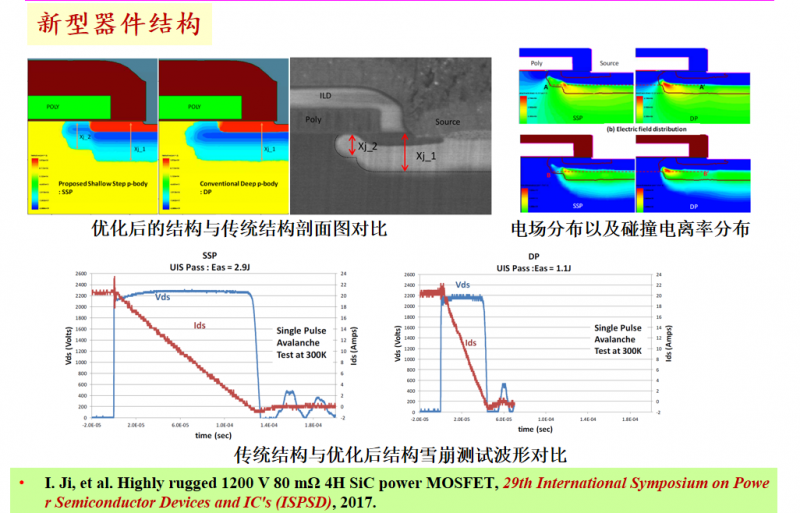

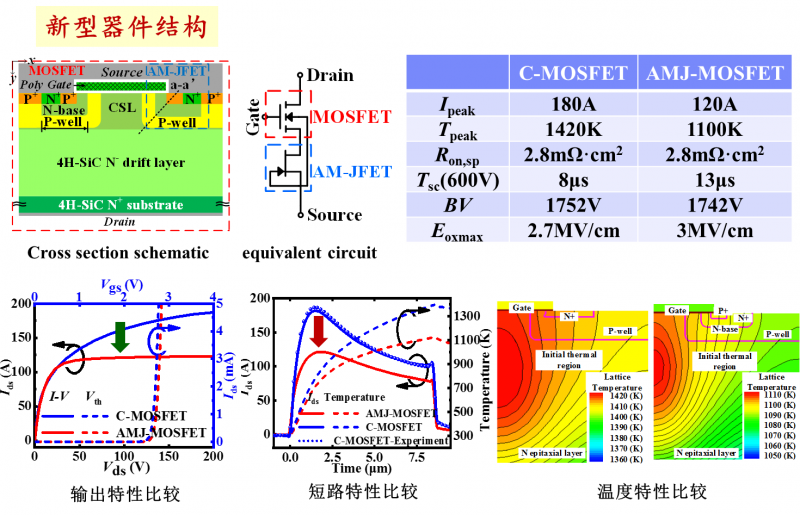

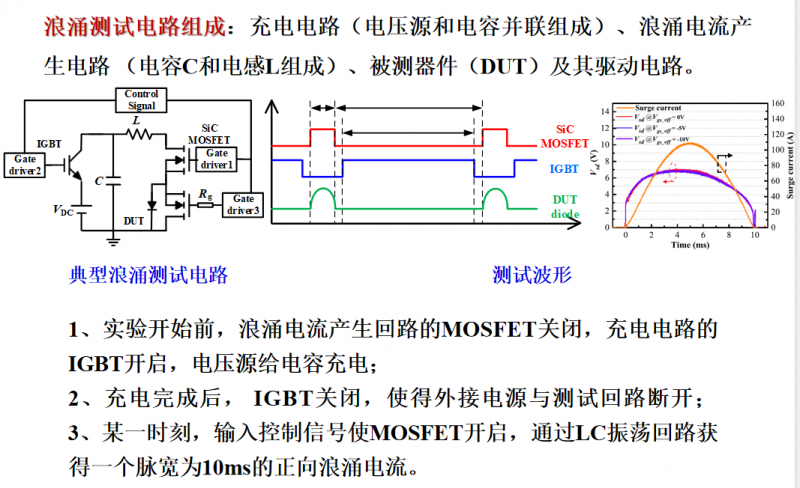

报告针对SiC MOSFET器件面临的极端应力下的动态鲁棒性问题,调研和评估了现阶段SiC MOSFET器件的失效模式和失效机理,包括单次可承受的最大应力以及多次重复应力后的器件参数退化程度,并且总结对比了目前已有研究中改善器件动态可靠性的结构和方案。同时,通过自主搭建的动态可靠性测试平台研究了SiC MOSFET器件短路特性、UIS特性和浪涌电流特性,研究对象涵盖了目前主流SiC MOSFET器件结构,包括平面栅结构(Planar Gate)、双沟槽栅结构(Double Trench Gate)和非对称沟槽栅(Asymmetric Trench Gate)结构,获得不同结构在不同应力下的失效能力和失效模式。通过半导体数值分析工具,较系统探讨了器件动态开关过程中的物理行为和失效机制,阐明了器件失效的内部物理机理和影响器件鲁棒性的关键因素。基于以上研究,提出了快速预测器件短路耐量模型和改善器件短路特性的集成自调节JFET器件新结构,对SiC MOSFET器件的设计和工程应用起到了良好的指导作用。

报告指出,目前国际上SiC功率器件面临的技术难度正在逐步降低,随着大尺寸SiC晶圆的发展,价格最终不会成为制约的瓶颈;在混合电动汽车、电动汽车以及智能电网等节能减排行业的大力牵引下,SiC功率器件正在逐步迈向普及化;

SiC功率器件的静态可靠性问题正在逐步解决;但是极端应力下的器件动态可靠性(失效模式、机理及其加固结构等)亟待深入研究。

嘉宾简介

邓小川,一直从事宽禁带半导体SiC功率器件理论模型、新结构、器件制备与可靠性研究,主持和承担了国家科技重大专项课题、国家自然科学基金重点/面上项目、国家重点研发计划子课题、国家重点实验室开放基金、国内外校企合作课题等20余项,在半导体功率器件领域顶级期刊IEEE Trans. Power Electronics、IEEE Electron Device Letter、IEEE Trans. Industrial Electronics、IEEE Trans. Electron Device以及本领域顶级会议ISPSD、ICSCRM等国际学术会议上发表论文80余篇;申请中国发明专利20余项,授权10余项,获得北京市科技发明二等奖。